# The development of reliable X-by-Wire systems: Assessing the effectiveness of a "simulation first" approach

Thesis submitted for the degree of Doctor of Philosophy at the University of Leicester

by

**Devaraj Ayavoo** B.Eng. (1<sup>st</sup> Hons.)

Embedded Systems Laboratory Department of Engineering University of Leicester Leicester, United Kingdom

September 2006

UMI Number: U217825

All rights reserved

INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI U217825 Published by ProQuest LLC 2013. Copyright in the Dissertation held by the Author. Microform Edition © ProQuest LLC. All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

# The development of reliable X-by-Wire systems: Assessing the effectiveness of a "simulation first" approach

### Devaraj Ayavoo

#### Abstract

Networks of embedded processors play an increasingly important role in the control of automotive, aerospace, industrial, defence and medical systems. The requirements for such "X-by-Wire" applications are highly demanding and complex in nature, and there are numerous possible design and technology options available. As a consequence, in all but the most trivial systems, engineering teams who wish to identify the "best" solution can only hope to prototype a small percentage of the possible designs.

Several researchers have argued that an effective solution to these problems is to use computer simulations in the early stages of the design process. The aim of this thesis is to explore the effectiveness of such a "simulation first" approach when developing X-by-Wire systems. The main focus is on the automotive sector, but it is suggested that the techniques developed during the course of this project can be more widely applied.

This document makes three main contributions, as follows.

First, it provides clear empirical evidence of the extent to which a "simulation first" approach can be used to support the development of non-trivial X-by-Wire systems.

Second, it introduces a novel, cost-effective empirical "small group methodology" (SGM) to compare between different development techniques for embedded systems. The SGM is described, and its effectiveness demonstrated in four non-trivial case studies.

Third, evidence is presented which suggests that the SGM may be more widely applicable.

# Acknowledgement

Firstly, I would like to express my deepest gratitude to my supervisor Dr. Michael Pont for his constant guidance and encouragement throughout this research project. I am very appreciative of all the help that you have provided and have thoroughly enjoyed working with you. You have made this "journey" of mine a very memorable one.

Next, I would like to thank the UK Government (Department of Education and Skills) for awarding me the ORS Scholarship. In addition, I would also like to thank Pi Technology, for partially funding my research project. In particular, I am grateful to Stephen Parker and Mike Ellims for their various useful contributions to the project.

This research project would not have been possible without the peer support of my colleagues in the Embedded Systems Laboratory. I thank you all for your encouragement, support and the occasional distraction. Also, a special thanks to all my colleagues from University of Leicester's Welfare Service. And to my good friends here and abroad, I thank you for your unwavering belief in me.

A special thanks to my uncle, Dr. Nadaraja Kannan, for encouraging me to pursue a doctorate degree.

Last but not least, I cannot thank my parents, sister and all my family members enough for their constant support and prayers over the last few years. Thank you for always being there for me. I dedicate this thesis to my parents and sister

Ayavoo Kannan, Gunabushany Munusamy & Nalini Ayavoo

# **Table of Contents**

| LIST OF CASE STUDIES                                                                                                                         | III                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF FIGURES                                                                                                                              | IV                                                                                                                                                                          |

| LIST OF TABLES                                                                                                                               | VI                                                                                                                                                                          |

| LIST OF PUBLICATIONS                                                                                                                         | VII                                                                                                                                                                         |

| LIST OF ABBREVIATIONS, SYMBOLS AND UNITS                                                                                                     | IX                                                                                                                                                                          |

| 1. INTRODUCTION                                                                                                                              | 1                                                                                                                                                                           |

| 1.1 INTRODUCTION                                                                                                                             |                                                                                                                                                                             |

| 1.2 DESCRIPTION OF THE PROBLEM                                                                                                               |                                                                                                                                                                             |

| 1.3 KEY CONTRIBUTIONS                                                                                                                        |                                                                                                                                                                             |

| 1.4 Thesis layout<br>1.5 Conclusions                                                                                                         |                                                                                                                                                                             |

| 2. WHAT SIMULATORS ARE AVAILABLE?                                                                                                            |                                                                                                                                                                             |

| 2.1 INTRODUCTION                                                                                                                             |                                                                                                                                                                             |

| 2.2 WHAT DO WE NEED TO SIMULATE?                                                                                                             |                                                                                                                                                                             |

| 2.3 AVAILABLE SIMULATION TOOLS                                                                                                               |                                                                                                                                                                             |

| 2.4 DISCUSSION                                                                                                                               |                                                                                                                                                                             |

| 2.5 CONCLUSIONS                                                                                                                              | 24                                                                                                                                                                          |

| 3. DOES THE TRUETIME SIMULATOR WORK?                                                                                                         | 26                                                                                                                                                                          |

| 3.1 INTRODUCTION                                                                                                                             | .26                                                                                                                                                                         |

| 3.2 CASE STUDY 3A: THE CRUISE-CONTROL SYSTEM                                                                                                 |                                                                                                                                                                             |

| 3.3 CASE STUDY 3B: THE INVERTED PENDULUM SYSTEM                                                                                              |                                                                                                                                                                             |

| 3.4 DISCUSSION AND CONCLUSIONS                                                                                                               | 40                                                                                                                                                                          |

| 4. HOW CAN WE ANSWER MORE SPECIFIC QUESTIONS ABOUT THE ROLE OF                                                                               |                                                                                                                                                                             |

| SIMULATION?                                                                                                                                  | 41                                                                                                                                                                          |

| SIMULATION?                                                                                                                                  |                                                                                                                                                                             |

| 4.1 INTRODUCTION                                                                                                                             | 41                                                                                                                                                                          |

| 4.1 Introduction<br>4.2 Challenges of empirical software studies                                                                             |                                                                                                                                                                             |

| 4.1 INTRODUCTION                                                                                                                             | 41<br>43<br>45                                                                                                                                                              |

| <ul> <li>4.1 INTRODUCTION</li> <li>4.2 CHALLENGES OF EMPIRICAL SOFTWARE STUDIES</li></ul>                                                    | 41<br>43<br>45<br>49<br>56                                                                                                                                                  |

| <ul> <li>4.1 INTRODUCTION</li> <li>4.2 CHALLENGES OF EMPIRICAL SOFTWARE STUDIES</li></ul>                                                    | 41<br>43<br>45<br>49<br>56                                                                                                                                                  |

| <ul> <li>4.1 INTRODUCTION</li> <li>4.2 CHALLENGES OF EMPIRICAL SOFTWARE STUDIES</li></ul>                                                    | 41<br>43<br>45<br>49<br>56<br>57                                                                                                                                            |

| <ul> <li>4.1 INTRODUCTION</li> <li>4.2 CHALLENGES OF EMPIRICAL SOFTWARE STUDIES</li></ul>                                                    | 41<br>43<br>45<br>49<br>56<br>57<br>57<br>58<br>58                                                                                                                          |

| <ul> <li>4.1 INTRODUCTION</li> <li>4.2 CHALLENGES OF EMPIRICAL SOFTWARE STUDIES</li></ul>                                                    | 41<br>43<br>45<br>49<br>56<br>57<br><b>58</b><br>58<br>59                                                                                                                   |

| <ul> <li>4.1 INTRODUCTION</li> <li>4.2 CHALLENGES OF EMPIRICAL SOFTWARE STUDIES</li></ul>                                                    | 41<br>43<br>45<br>49<br>56<br>57<br>58<br>58<br>58<br>58<br>59<br>63                                                                                                        |

| <ul> <li>4.1 INTRODUCTION</li></ul>                                                                                                          | 41<br>43<br>45<br>49<br>56<br>57<br>58<br>58<br>58<br>59<br>63<br>65                                                                                                        |

| <ul> <li>4.1 INTRODUCTION</li> <li>4.2 CHALLENGES OF EMPIRICAL SOFTWARE STUDIES</li></ul>                                                    | 41<br>43<br>45<br>49<br>56<br>57<br><b>58</b><br>58<br>58<br>59<br>63<br>65<br>70                                                                                           |

| <ul> <li>4.1 INTRODUCTION</li></ul>                                                                                                          | 41<br>43<br>45<br>49<br>56<br>57<br>58<br>58<br>58<br>59<br>63<br>63<br>65<br>70<br>72                                                                                      |

| <ul> <li>4.1 INTRODUCTION</li> <li>4.2 CHALLENGES OF EMPIRICAL SOFTWARE STUDIES</li></ul>                                                    | 41<br>43<br>45<br>49<br>56<br>57<br>58<br>58<br>58<br>59<br>63<br>65<br>70<br>72<br>72<br>73                                                                                |

| <ul> <li>4.1 INTRODUCTION.</li> <li>4.2 CHALLENGES OF EMPIRICAL SOFTWARE STUDIES.</li> <li>4.3 TOWARDS A "SMALL GROUP" METHODOLOGY</li></ul> | 41<br>43<br>45<br>49<br>56<br>57<br><b>58</b><br>58<br>58<br>59<br>63<br>63<br>65<br>70<br>72<br>72<br>73<br>73<br>74                                                       |

| <ul> <li>4.1 INTRODUCTION</li></ul>                                                                                                          | 41<br>43<br>45<br>49<br>56<br>57<br><b>58</b><br>58<br>58<br>58<br>59<br>63<br>65<br>70<br>72<br>72<br>73<br>73<br>74<br>74                                                 |

| <ul> <li>4.1 INTRODUCTION</li></ul>                                                                                                          | 41<br>43<br>45<br>49<br>56<br>57<br>58<br>58<br>58<br>58<br>59<br>63<br>65<br>70<br>72<br>72<br>73<br>73<br>74<br>78                                                        |

| <ul> <li>4.1 INTRODUCTION</li></ul>                                                                                                          | 41<br>43<br>45<br>49<br>56<br>57<br>58<br>58<br>58<br>58<br>59<br>63<br>65<br>70<br>72<br>72<br>73<br>73<br>73<br>74<br>78<br>80                                            |

| <ul> <li>4.1 INTRODUCTION</li></ul>                                                                                                          | 41<br>43<br>45<br>49<br>56<br>57<br>58<br>58<br>58<br>59<br>63<br>63<br>65<br>70<br>72<br>72<br>73<br>73<br>74<br>74<br>76<br>78<br>80<br>80<br>86                          |

| <ul> <li>4.1 INTRODUCTION</li></ul>                                                                                                          | 41<br>43<br>45<br>49<br>56<br>57<br>58<br>58<br>58<br>58<br>59<br>63<br>63<br>65<br>70<br>70<br>72<br>73<br>73<br>73<br>74<br>74<br>76<br>78<br>80<br>86<br>90              |

| <ul> <li>4.1 INTRODUCTION</li></ul>                                                                                                          | 41<br>43<br>45<br>49<br>56<br>57<br><b>58</b><br>58<br>59<br>63<br>63<br>65<br>70<br>70<br>72<br>73<br>73<br>74<br>74<br>76<br>78<br>80<br>80<br>86<br>90<br>90<br>91<br>91 |

| 7.3 CASE STUDY 7: EVALUATION OF SOFTWARE QUALITY                              |       |

|-------------------------------------------------------------------------------|-------|

| 7.4 THE MEASUREMENT OF QUALITY INDICATORS                                     |       |

| 7.5 ANALYSIS OF THE RESULTS FROM CASE STUDY 7                                 |       |

| 7.6 DISCUSSION                                                                |       |

| 7.7 CONCLUSIONS                                                               |       |

| 8. CAN THE SGM BE APPLIED MORE WIDELY?                                        |       |

| 8.1 INTRODUCTION                                                              |       |

| 8.2 CASE STUDY 8: EVALUATION OF THE PTTES BUILDER                             |       |

| 8.3 ANALYSIS OF THE RESULTS FOR CASE STUDY 8                                  |       |

| 8.4 DISCUSSION                                                                |       |

| 8.5 CONCLUSIONS                                                               |       |

| 9. DISCUSSION AND CONCLUSIONS                                                 |       |

| 9.1 INTRODUCTION                                                              |       |

| 9.2 OVERVIEW OF THE WORK CONDUCTED                                            |       |

| 9.3 SIMULATION IN PRACTICE                                                    |       |

| 9.4 EVALUATION OF THE SGM                                                     |       |

| 9.5 OTHER "BY PRODUCTS" OF THE RESEARCH PROJECT                               |       |

| 9.6 FUTURE WORK                                                               |       |

| 9.7 CONCLUSIONS                                                               |       |

| REFERENCES                                                                    |       |

| APPENDICES                                                                    |       |

| APPENDIX-A OBSERVING THE DEVELOPMENT OF RELIABLE EMBEDDED SYSTEMS             | A-1   |

| APPENDIX-B TWO NOVEL SHARED-CLOCK SCHEDULING ALGORITHMS FOR USE WITH CAN-     | BASED |

| DISTRIBUTED SYSTEMS                                                           | B-1   |

| APPENDIX-C A 'HARDWARE-IN-THE-LOOP' TESTBED REPRESENTING THE OPERATION OF A G |       |

| SYSTEM IN A PASSENGER CAR                                                     |       |

| APPENDIX-D BACKGROUND ON DESIGN PATTERNS                                      |       |

| APPENDIX-E COMPARISON OF EFFORT AND SOURCE CODE CHANGES                       |       |

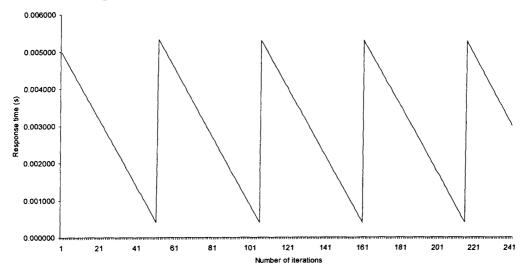

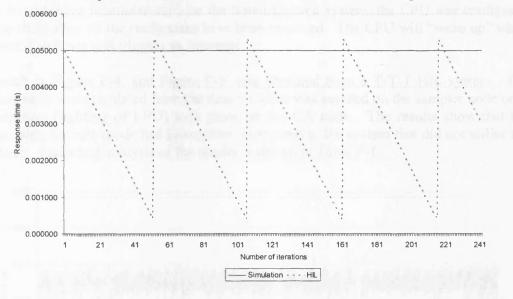

| APPENDIX-F LIMITATIONS OF THE TRUETIME SIMULATOR                              |       |

| APPENDIX-G TESTCASES FOR CASE STUDY 8                                         | G-1   |

# **List of Case Studies**

| CASE STUDY 3A THE AUTOMOTIVE CRUISE-CONTROL SYSTEM        | 27  |

|-----------------------------------------------------------|-----|

| CASE STUDY 3B THE INVERTED PENDULUM SYSTEM                | 35  |

| CASE STUDY 5 ASSESSING THE EFFORT INVOLVED                | 59  |

| CASE STUDY 6 EVALUATION OF THE NEW SIMULATION METHODOLOGY | 76  |

| CASE STUDY 7 EVALUATION OF SOFTWARE QUALITY               | .93 |

| CASE STUDY 8 EVALUATION OF THE PTTES BUILDER1             | 05  |

# List of Figures

| FIGURE 1-1 MICROCONTROLLER IMPLEMENTATION GROWTH IN AUTOMOBILES. REDRAWN FROM DATA IN BANNATYNE (2003), FIGURE 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 1-2 AN ILLUSTRATION OF AN X-BY-WIRE SYSTEM IN A CAR FROM BRETZ (2001), FIGURE 1.<br>COPYRIGHT IEEE, REPRODUCED WITH PERMISSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

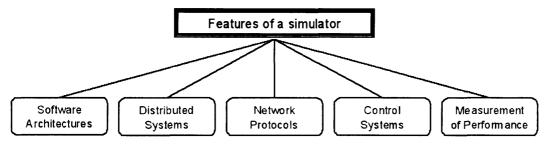

| FIGURE 2-1 REQUIRED FEATURES OF A TOOL TO SIMULATE X-BY-WIRE SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

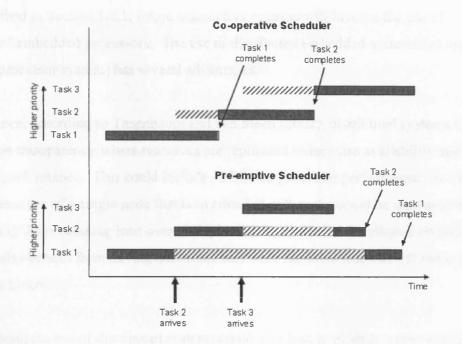

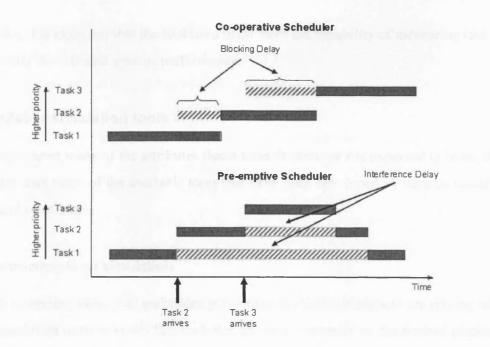

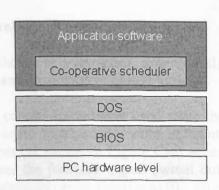

| FIGURE 2-2 TASK EXECUTION FOR CO-OPERATIVE AND PRE-EMPTIVE SCHEDULERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

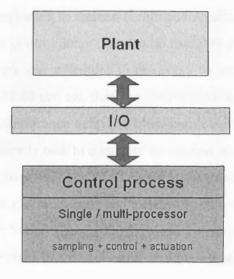

| FIGURE 2-3 THE PLANT, CONTROL PROCESS AND I/OS FOR A CONTROL SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FIGURE 2-4 EXAMPLES OF BLOCKING AND INTERFERENCE DELAY FOR CO-OPERATIVE AND PRE-EMPTIVE SCHEDULERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

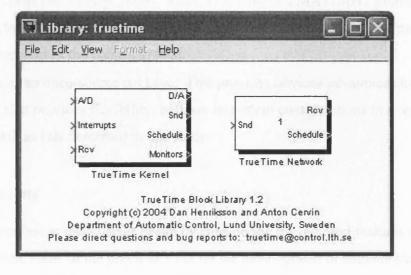

| FIGURE 2-5 THE TRUETIME SIMULATION LIBRARY ON SIMULINK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

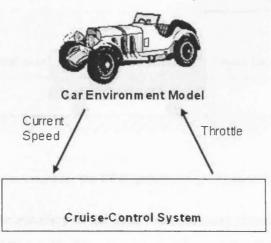

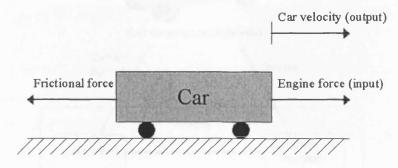

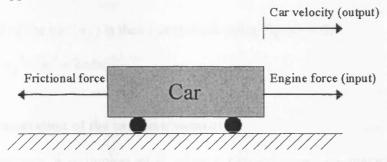

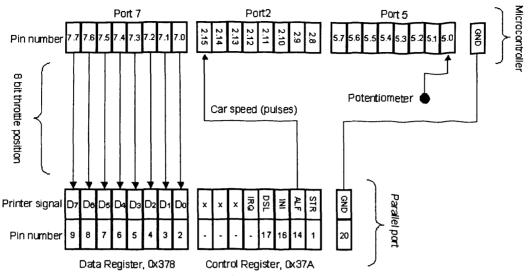

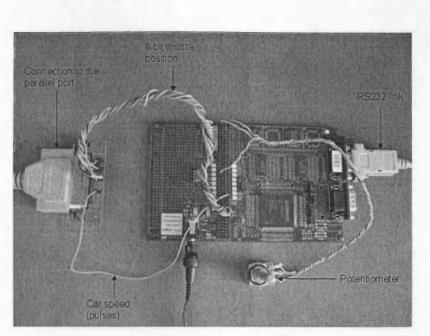

| FIGURE 3-1 A BASIC CRUISE-CONTROL SYSTEM FOR CASE STUDY 3A (ADAPTED FROM AYAVOO <i>ET AL.</i> 2004,<br>FIGURE 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

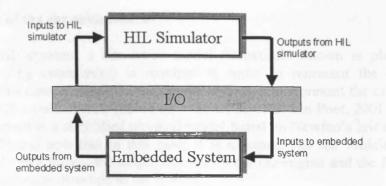

| FIGURE 3-2 THE CAR ENVIRONMENT FOR THE CCS (ADAPTED FROM AYAVOO ET AL. 2005C, FIGURE 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

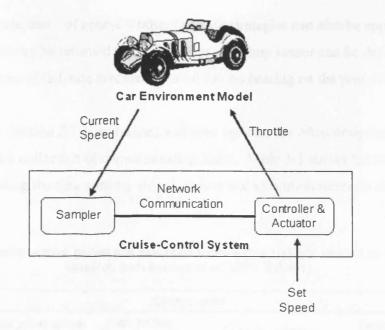

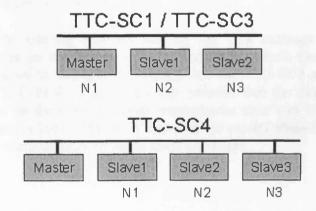

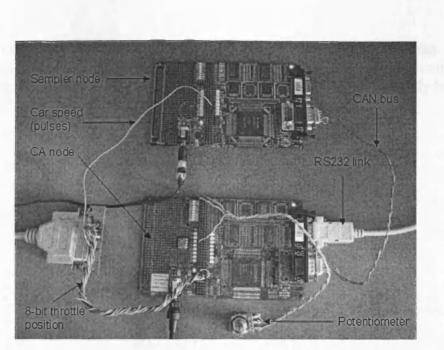

| FIGURE 3-3 A DISTRIBUTED CRUISE-CONTROL SYSTEM FOR CASE STUDY 3A (ADAPTED FROM AYAVOO <i>ET AL.</i> 2004, FIGURE 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

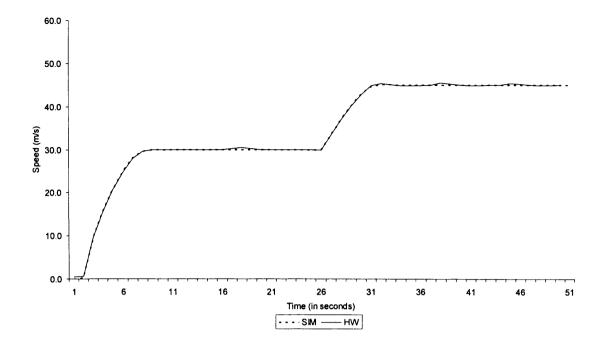

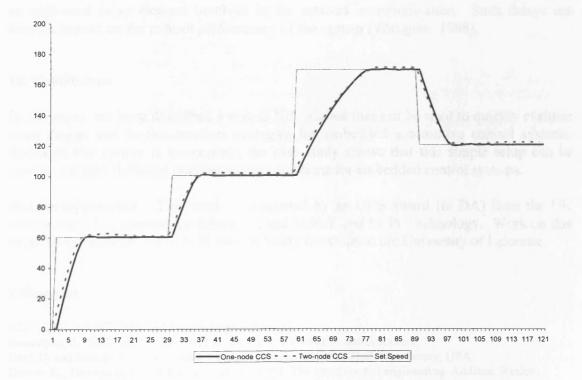

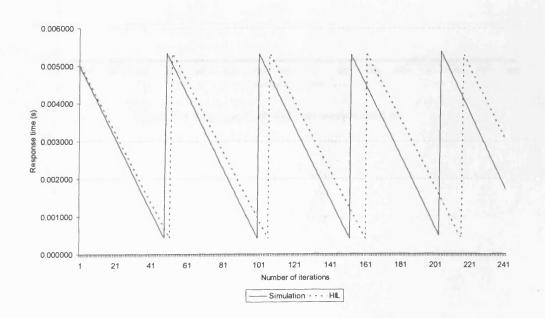

| FIGURE 3-4 CONTROL PERFORMANCE USING THE TRUETIME SIMULATOR AND HIL TESTBED FOR CASE STUDY<br>3A (ADAPTED FROM AYAVOO <i>ET AL</i> . 2004, FIGURE 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

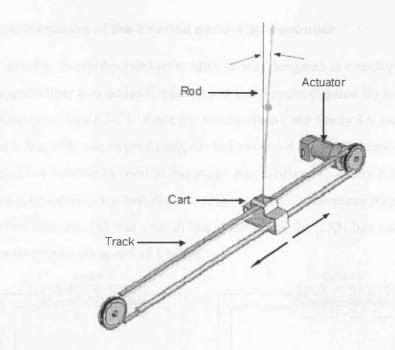

| FIGURE 3-5 THE TESTBED OF AN INVERTED PENDULUM FOR CASE STUDY 3B (ADAPTED FROM BAUTISTA <i>ET AL.</i> , 2005, FIGURE 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

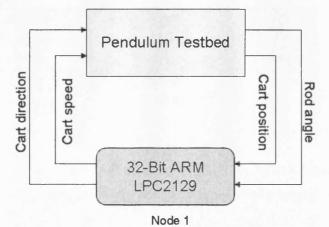

| FIGURE 3-6 THE INPUT/OUTPUT OF THE PENDULUM TESTBED (PLANT) AND THE ARM MICROCONTROLLER FOR<br>CASE STUDY 3B. FIGURE ADAPTED FROM AYAVOO <i>et al.</i> 2006, Fig. 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

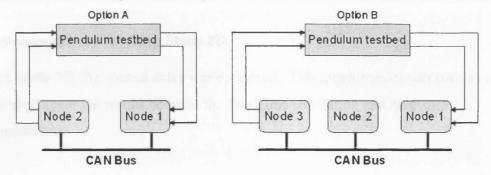

| FIGURE 3-7 DISTRIBUTED IMPLEMENTATION OPTIONS FOR THE PENDULUM CONTROL IN CASE STUDY 3B 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

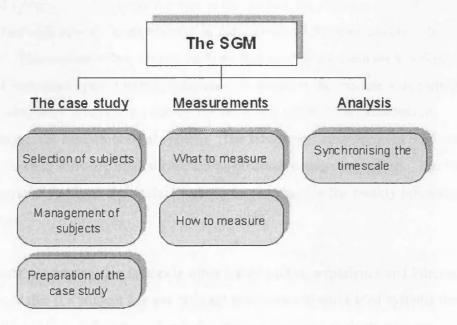

| FIGURE 4-1 OVERVIEW OF THE SGM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

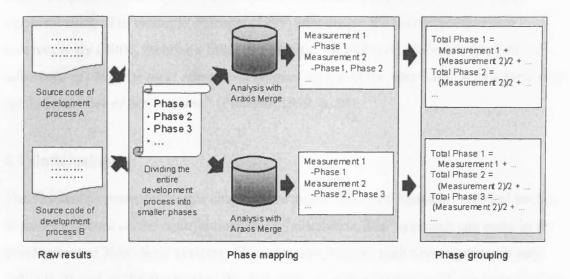

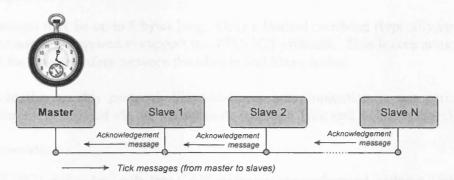

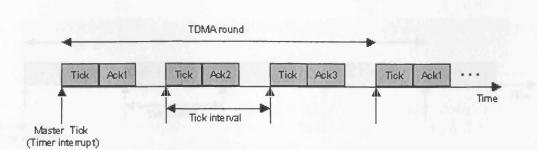

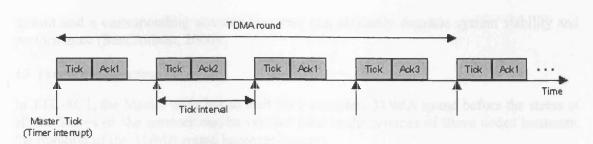

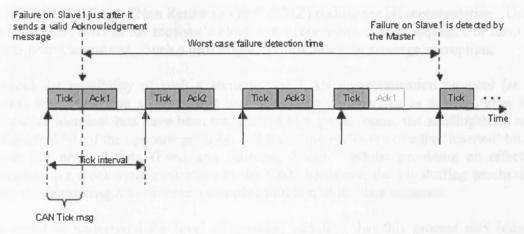

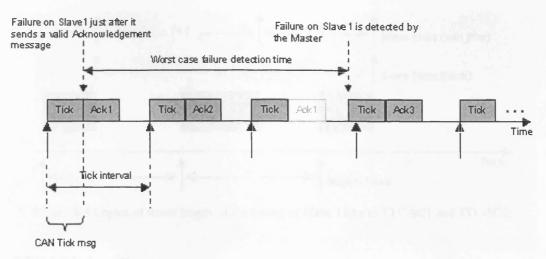

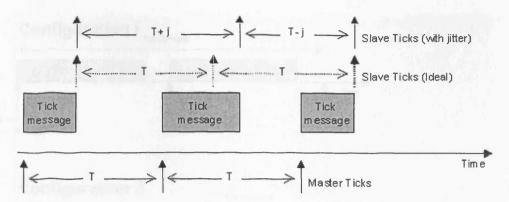

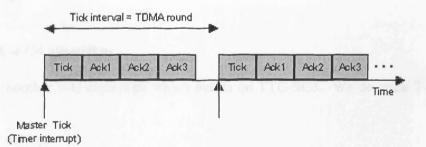

| FIGURE 4-2 THE SYNCHRONISATION TECHNIQUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

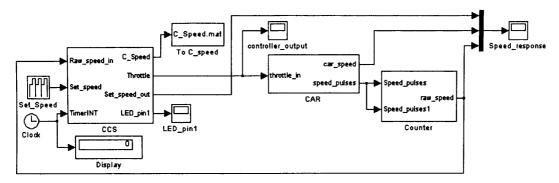

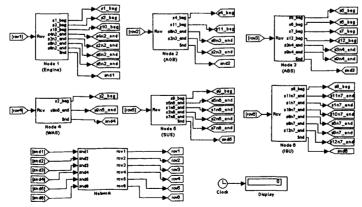

| FIGURE 5-1 THE CONTROL SYSTEM SETUP ON TRUETIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FIGURE 5-1 THE CONTROL SYSTEM SETUP ON TRUETIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

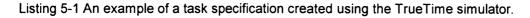

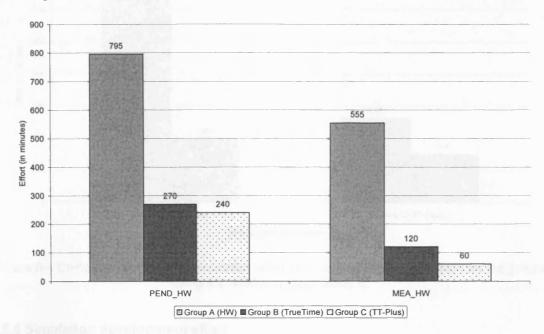

| FIGURE 5-2 TOTAL HARDWARE IMPLEMENTATION TIME FOR ALL THE GROUPS IN CASE STUDY 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FIGURE 5-2 TOTAL HARDWARE IMPLEMENTATION TIME FOR ALL THE GROUPS IN CASE STUDY 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FIGURE 5-2 TOTAL HARDWARE IMPLEMENTATION TIME FOR ALL THE GROUPS IN CASE STUDY 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

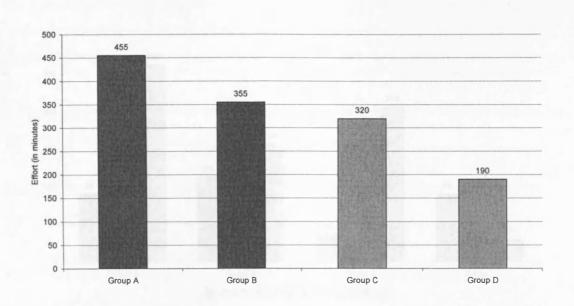

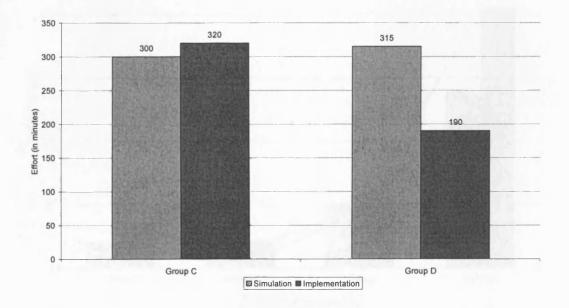

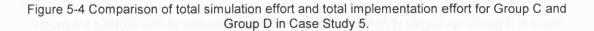

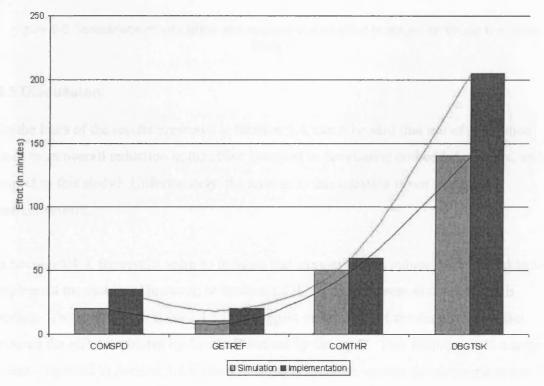

| FIGURE 5-2 TOTAL HARDWARE IMPLEMENTATION TIME FOR ALL THE GROUPS IN CASE STUDY 5.       67         FIGURE 5-3 HARDWARE IMPLEMENTATION EFFORT IN STAGES FOR THE FOUR GROUPS IN CASE STUDY 5.       68         FIGURE 5-4 COMPARISON OF TOTAL SIMULATION EFFORT AND TOTAL IMPLEMENTATION EFFORT FOR GROUP C       68         FIGURE 5-5 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP C IN CASE       69         FIGURE 5-6 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP D IN CASE       69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FIGURE 5-2 TOTAL HARDWARE IMPLEMENTATION TIME FOR ALL THE GROUPS IN CASE STUDY 5.       67         FIGURE 5-3 HARDWARE IMPLEMENTATION EFFORT IN STAGES FOR THE FOUR GROUPS IN CASE STUDY 5.       68         FIGURE 5-4 COMPARISON OF TOTAL SIMULATION EFFORT AND TOTAL IMPLEMENTATION EFFORT FOR GROUP C AND GROUP D IN CASE STUDY 5.       68         FIGURE 5-5 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP C IN CASE STUDY 5.       69         FIGURE 5-6 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP D IN CASE STUDY 5.       69         FIGURE 5-6 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP D IN CASE STUDY 5.       70                                                                                                                                                                                                                                                                                                                                            |

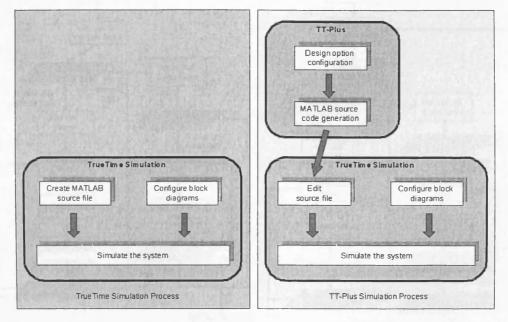

| FIGURE 5-2 TOTAL HARDWARE IMPLEMENTATION TIME FOR ALL THE GROUPS IN CASE STUDY 5.       67         FIGURE 5-3 HARDWARE IMPLEMENTATION EFFORT IN STAGES FOR THE FOUR GROUPS IN CASE STUDY 5.       68         FIGURE 5-4 COMPARISON OF TOTAL SIMULATION EFFORT AND TOTAL IMPLEMENTATION EFFORT FOR GROUP C AND GROUP D IN CASE STUDY 5.       68         FIGURE 5-5 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP C IN CASE STUDY 5.       69         FIGURE 5-6 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP D IN CASE STUDY 5.       70         FIGURE 6-1 COMPARISON OF TRUETIME AND TT-PLUS SIMULATION PROCESS.       75         FIGURE 6-2 A FLOWCHART DESCRIBING HOW TT-PLUS LEADS THE USER THROUGH THE VARIOUS       70                                                                                                                                                                                                                                                                             |

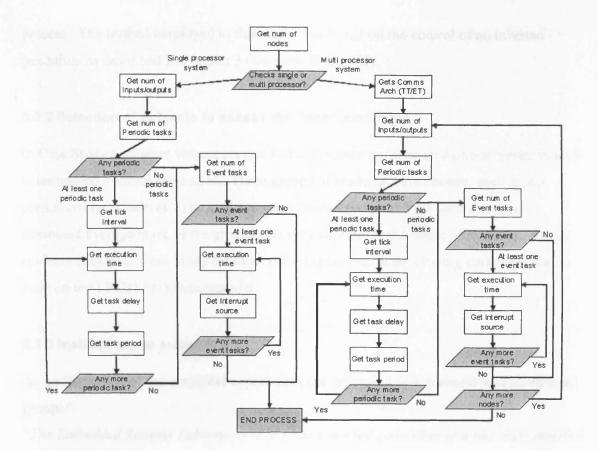

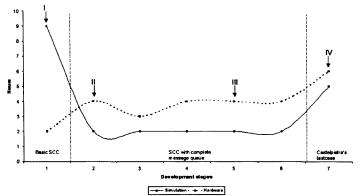

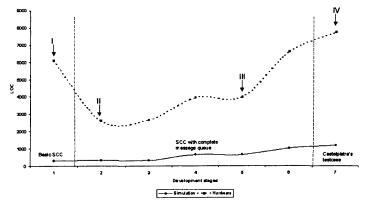

| FIGURE 5-2 TOTAL HARDWARE IMPLEMENTATION TIME FOR ALL THE GROUPS IN CASE STUDY 5.       67         FIGURE 5-3 HARDWARE IMPLEMENTATION EFFORT IN STAGES FOR THE FOUR GROUPS IN CASE STUDY 5.       68         FIGURE 5-4 COMPARISON OF TOTAL SIMULATION EFFORT AND TOTAL IMPLEMENTATION EFFORT FOR GROUP C AND GROUP D IN CASE STUDY 5.       68         FIGURE 5-5 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP C IN CASE STUDY 5.       69         FIGURE 5-6 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP D IN CASE STUDY 5.       70         FIGURE 6-1 COMPARISON OF TRUETIME AND TT-PLUS SIMULATION PROCESS.       75         FIGURE 6-2 A FLOWCHART DESCRIBING HOW TT-PLUS LEADS THE USER THROUGH THE VARIOUS IMPLEMENTATION OPTIONS.       76         FIGURE 6-3 HARDWARE IMPLEMENTATION EFFORT FOR DIFFERENT STAGES (CASE STUDY 6). FIGURE       70                                                                                                                                              |

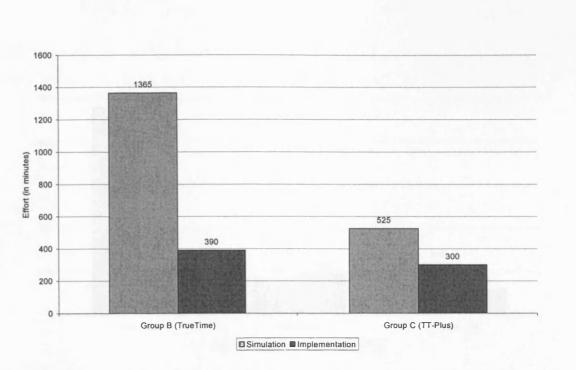

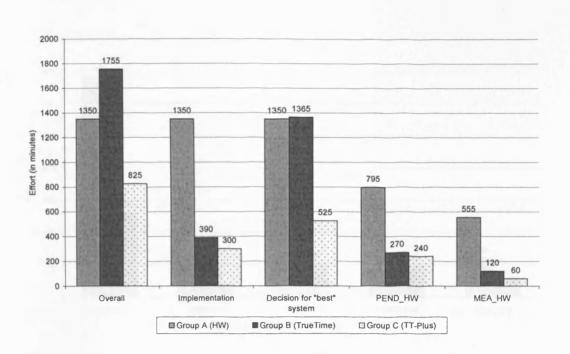

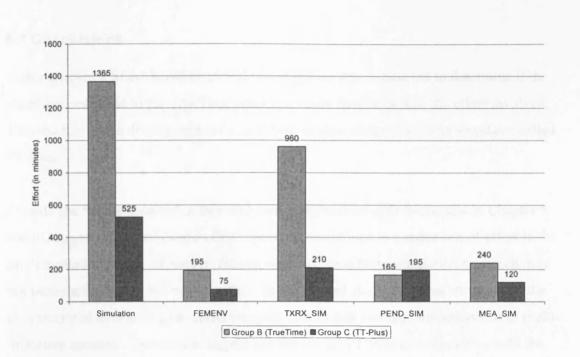

| FIGURE 5-2 TOTAL HARDWARE IMPLEMENTATION TIME FOR ALL THE GROUPS IN CASE STUDY 5.       67         FIGURE 5-3 HARDWARE IMPLEMENTATION EFFORT IN STAGES FOR THE FOUR GROUPS IN CASE STUDY 5.       68         FIGURE 5-4 COMPARISON OF TOTAL SIMULATION EFFORT AND TOTAL IMPLEMENTATION EFFORT FOR GROUP C       68         FIGURE 5-5 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP C IN CASE       69         FIGURE 5-6 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP D IN CASE       69         FIGURE 5-6 COMPARISON OF SIMULATION AND IMPLEMENTATION EFFORT IN STAGES FOR GROUP D IN CASE       70         FIGURE 6-1 COMPARISON OF TRUETIME AND TT-PLUS SIMULATION PROCESS.       75         FIGURE 6-2 A FLOWCHART DESCRIBING HOW TT-PLUS LEADS THE USER THROUGH THE VARIOUS       76         FIGURE 6-3 HARDWARE IMPLEMENTATION EFFORT FOR DIFFERENT STAGES (CASE STUDY 6). FIGURE       76         FIGURE 6-4 COMPARISON OF THE TOTAL SIMULATION EFFORT FOR THE USER THROUGH THE VARIOUS       83 |

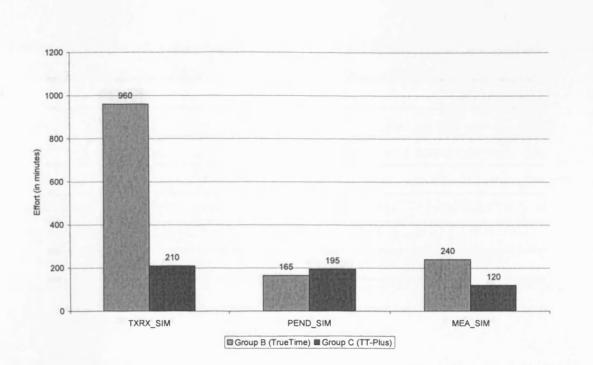

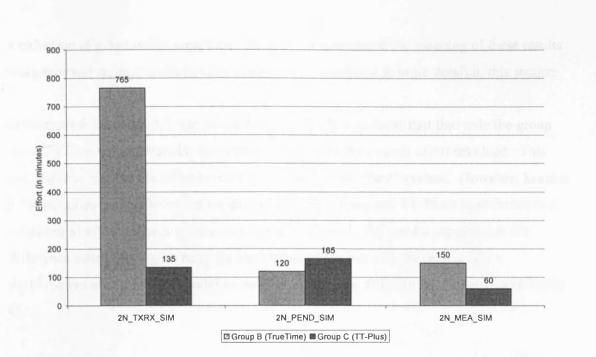

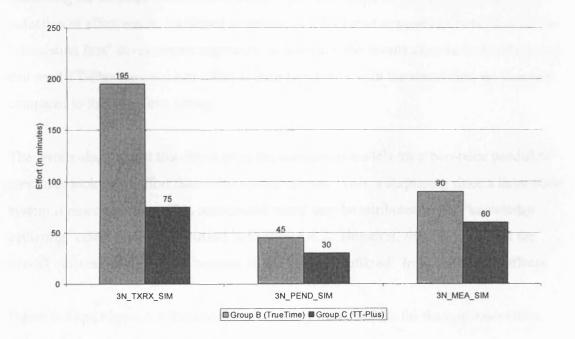

| FIGURE 6-7 THE SIMULATION EFFORT INVOLVED AT DIFFERENT PHASES FOR A THREE-NODE SYSTEM (CASE STUDY 6). FIGURE ADAPTED FROM AYAVOO <i>ET AL.</i> (2006), FIG. 6 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 6-8 SUMMARY OF THE IMPLEMENTATION EFFORT INVOLVED IN CASE STUDY 6                                                                                      |

| FIGURE 6-9 SUMMARY OF THE SIMULATION EFFORT INVOLVED IN CASE STUDY 6                                                                                          |

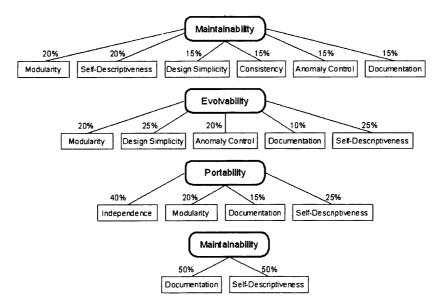

| FIGURE 7-1 AN EXAMPLE OF A FRAMEWORK FOR SOFTWARE QUALITY. REDRAWN FROM DATA IN MARTIN AND SHAFER (1996), FIGURE 3                                            |

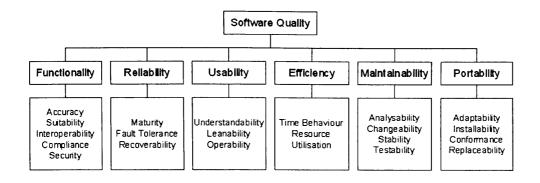

| FIGURE 7-2 THE ISO/IEC 9126 SOFTWARE QUALITY CHARACTERISTICS FROM A USER'S PERSPECTIVE.<br>REDRAWN FROM DATA IN BEVAN (1999), FIG. 1                          |

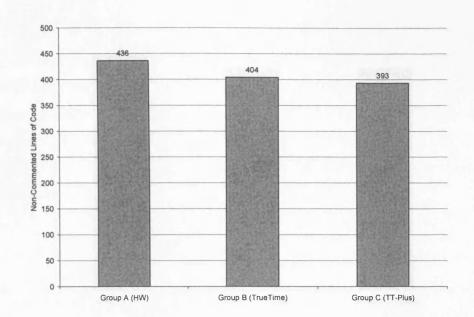

| FIGURE 7-3 RESULTS OF THE IMPLEMENTED LINES OF CODE FOR EACH GROUP IN CASE STUDY 7                                                                            |

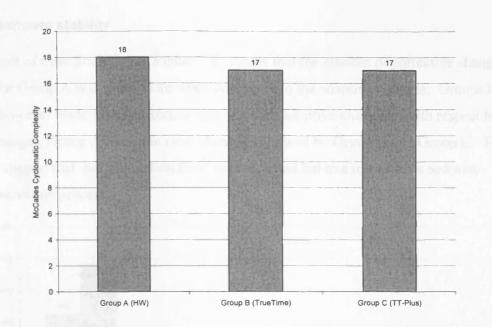

| FIGURE 7-4 RESULTS OF MCCABE'S CYCLOMATIC COMPLEXITY FOR EACH GROUP IN CASE STUDY 7 100                                                                       |

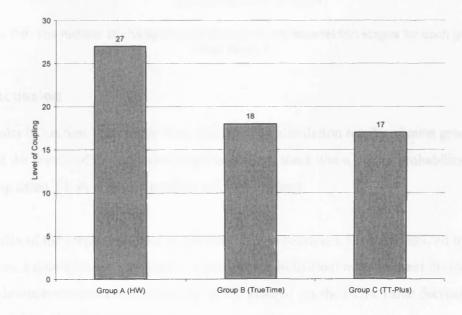

| FIGURE 7-5 THE LEVEL OF SOURCE CODE COUPLING FOR EACH GROUP IN CASE STUDY 7                                                                                   |

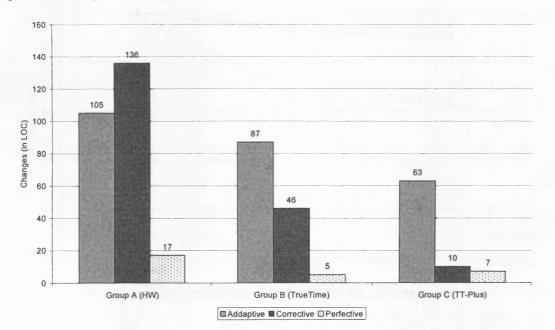

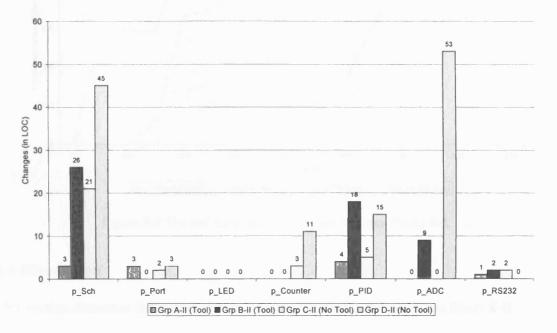

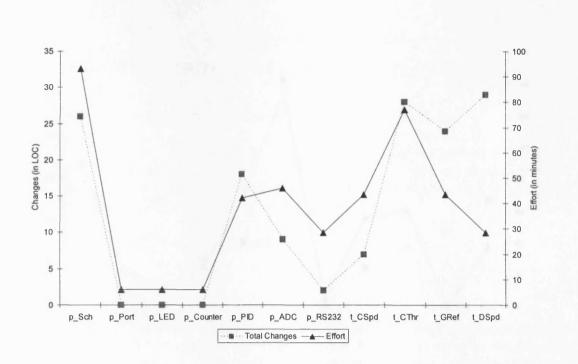

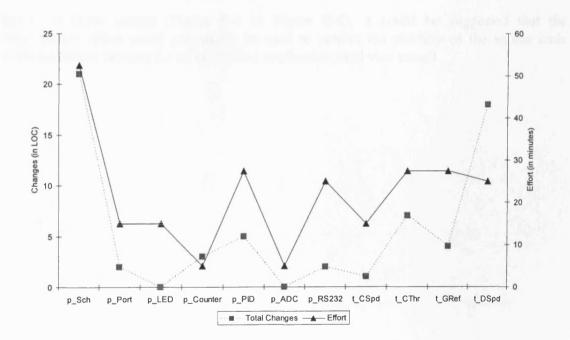

| FIGURE 7-6. THE NUMBER OF CHANGES MADE DURING THE IMPLEMENTATION STAGES FOR EACH GROUP IN<br>CASE STUDY 7                                                     |

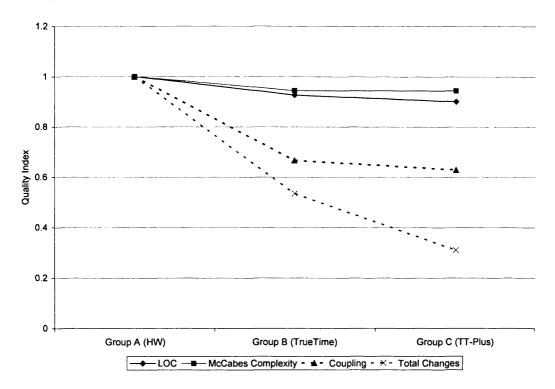

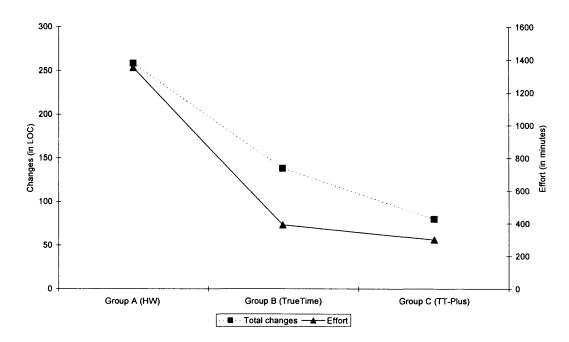

| FIGURE 7-7 TREND OF THE OVERALL RESULTS OF SOFTWARE QUALITY FOR A TWO-NODE SYSTEM IN CASE<br>STUDY 7                                                          |

| FIGURE 7-8 TREND OF CHANGES MADE AND IMPLEMENTATION EFFORT FOR ALL THE GROUPS IN CASE STUDY<br>7                                                              |

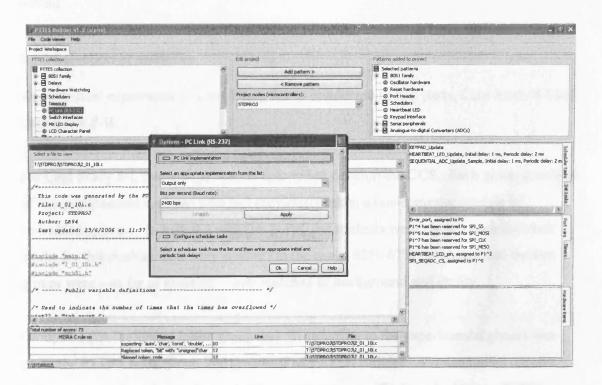

| FIGURE 8-1 EXAMPLE OF THE USER INTERFACE FOR THE PTTES BUILDER                                                                                                |

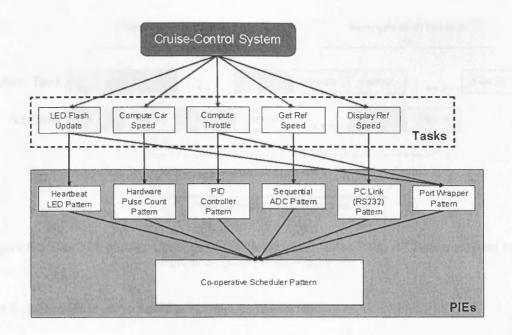

| FIGURE 8-2 DEVELOPING THE CCS USING THE ASSOCIATED PIES FOR CASE STUDY 8. FIGURE ADAPTED FROM PONT <i>ET AL.</i> (SUBMITTED), FIGURE 15                       |

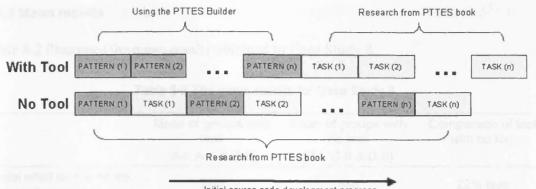

| FIGURE 8-3 THE CCS DEVELOPMENT PHASES FOR THE TEAMS IN CASE STUDY 8. FIGURE ADAPTED FROM<br>PONT <i>ET AL</i> . (SUBMITTED), FIGURE 16                        |

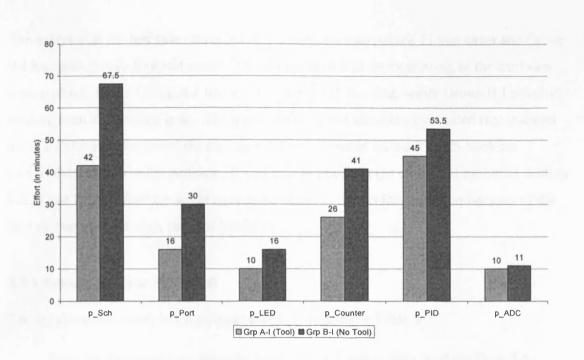

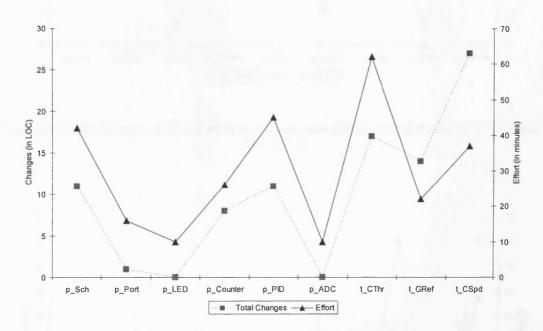

| FIGURE 8-4 EFFORT INVOLVED IN IMPLEMENTING THE RELATED PATTERNS IN CASE STUDY 8-1114                                                                          |

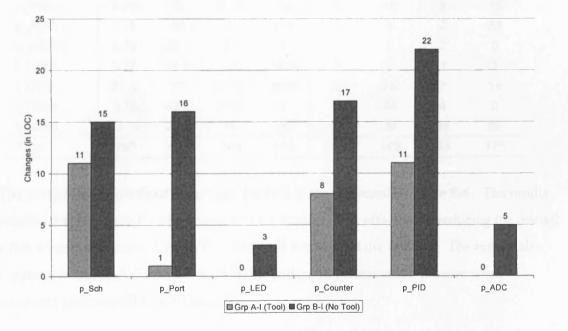

| FIGURE 8-5 THE NUMBER OF CHANGES MADE TO THE INDIVIDUAL PATTERNS IN CASE STUDY 8-1                                                                            |

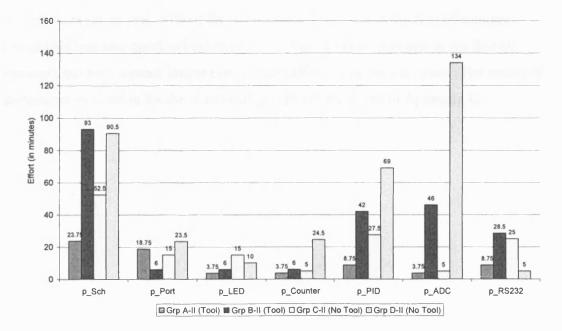

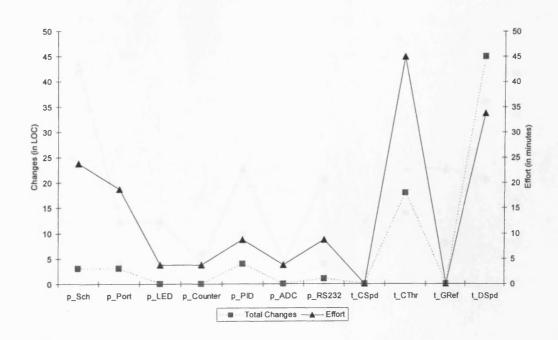

| FIGURE 8-6 THE EFFORT INVOLVED IN IMPLEMENTING THE RELATED PATTERNS IN CASE STUDY 8-II                                                                        |

| FIGURE 8-7 THE NUMBER OF CHANGES MADE TO THE INDIVIDUAL PATTERNS IN CASE STUDY 8-II                                                                           |

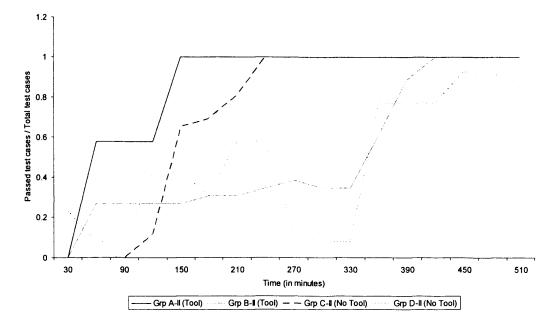

| FIGURE 8-8 THE TEST CASE COMPLIANCE RATIO IN CASE STUDY 8-II                                                                                                  |

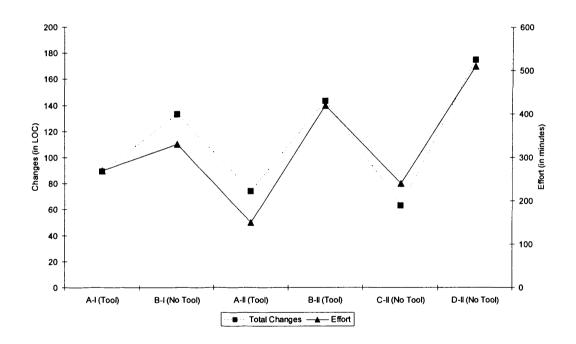

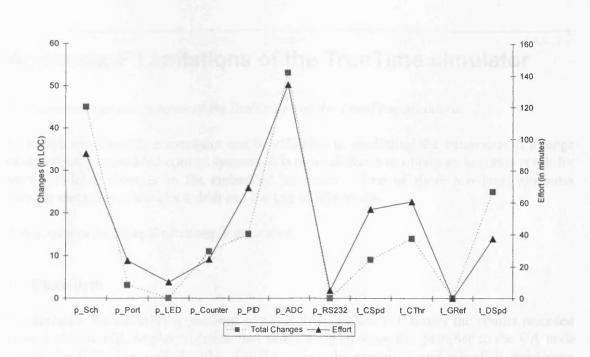

| FIGURE 8-9 TREND OF CHANGES MADE AND DEVELOPMENT EFFORT FOR ALL THE GROUPS IN CASE STUDY 8.                                                                   |

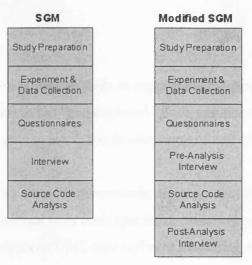

| FIGURE 9-1 THE MODIFIED SGM THAT INCORPORATES PRE- AND POST-ANALYSIS INTERVIEWS                                                                               |

# List of Tables

| TABLE 2-1 SOME DIFFERENCES IN THE CHARACTERISTICS OF THE COMPETING NETWORK PROTOCOLS IN THE AUTOMOTIVE SECTOR FOR SAFETY-CRITICAL APPLICATIONS (ORIGINAL SOURCES OBTAINED FROM KOPETZ, 2001; LEEN AND HEFFERNAN, 2002; MAIER <i>ET AL.</i> , 2002).         15                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TABLE 3-1 TASK INITIAL ARRIVAL, PERIOD AND EXECUTION TIMES WITH A 1MS TICK INTERVAL FOR CASE         STUDY 3A (ADAPTED FROM AYAVOO <i>et al.</i> 2004, Table 1)                                                                                                                                                                                           |

| TABLE 3-2 COMBINATION OF THE POSSIBLE IMPLEMENTATIONS FOR THE CCS IN CASE STUDY 3A (ADAPTED FROM AYAVOO <i>et al.</i> 2004, Table 2).         32                                                                                                                                                                                                          |

| TABLE 3-3 COMPARISON OF TRUETIME SIMULATION RESULTS AND THE HIL TESTBED OF AN "EVENT<br>MESSAGE" RESPONSE TIME (IN μS) FOR CASE STUDY 3A (ADAPTED FROM AYAVOO <i>ET AL.</i> 2004, TABLE<br>3).                                                                                                                                                            |

| TABLE 3-4 COMPARISON OF CONTROL DELAY (IN μS) BETWEEN THE TRUETIME SIMULATOR AND THE HIL TESTBED FOR CASE STUDY 3A (ADAPTED FROM AYAVOO <i>et al.</i> 2004, Table 4)                                                                                                                                                                                      |

| TABLE 3-5 THE PERCENTAGE OF MEAN DEVIATION BETWEEN THE TRUETIME SIMULATOR AND THE HIL         TESTBED FOR THE PERIODIC CONTROL TASKS IN CASE STUDY 3A (ADAPTED FROM AYAVOO <i>et al.</i> 2004, TABLE 5).                                                                                                                                                  |

| TABLE 3-6 TASK STRUCTURE OF THE PENDULUM CONTROLLER FOR CASE STUDY 3B.       39                                                                                                                                                                                                                                                                           |

| TABLE 3-7 COMPARISON OF THE CONTROL DELAY (IN MS) BETWEEN THE TRUETIME SIMULATION AND<br>IMPLEMENTATION FOR CASE STUDY 3B                                                                                                                                                                                                                                 |

| TABLE 4-1 "PROGRESS FORM" TO CATEGORISE THE ACTIVITIES UNDERTAKEN BY THE STUDENTS DURING THE<br>EXPERIMENT. GENERALLY, A TICK IS MARKED ON THE RELEVANT BOX TO INDICATE THAT "ACTIVITY X"<br>IS BEING CARRIED OUT AT A PARTICULAR TIME SLOT. NOTES WERE ALSO MADE TO RECORD ANY<br>DIFFICULTIES AND ANOMALIES OBSERVED THROUGHOUT THE DEVELOPMENT PROCESS |

| TABLE 5-1 GROUP STRUCTURE FOR CASE STUDY 5. TABLE ADAPTED FROM AYAVOO ET AL. (SUBMITTED),         TABLE II                                                                                                                                                                                                                                                |

| TABLE 5-2 RESULTS FOR CASE STUDY 5 AFTER EACH VERSION WAS MAPPED TO ITS CORRESPONDING PHASE         AND ITS RESPECTIVE TIME TAKEN IN MINUTES                                                                                                                                                                                                              |

| TABLE 5-3 RESULTS (IN MINUTES) FOR CASE STUDY 5 AFTER GROUPING VERSIONS TOGETHER. TABLE         ADAPTED FROM AYAVOO <i>ET AL.</i> (SUBMITTED), TABLE III.                                                                                                                                                                                                 |

| TABLE 5-4 THE MEAN RESULTS FOR EFFORT (IN MINUTES) FOR CASE STUDY 5. TABLE ADAPTED FROM         AYAVOO ET AL. (SUBMITTED), TABLE IV.                                                                                                                                                                                                                      |

| TABLE 6-1 DEVELOPMENT METHODOLOGY FOR EACH GROUP IN CASE STUDY 6. TABLE ADAPTED FROM         AYAVOO ET AL. (2006), TABLE 1                                                                                                                                                                                                                                |

| TABLE 6-2 SYNCHRONISED RESULTS FOR CASE STUDY 6 AFTER GROUPING SIMILAR PHASES TOGETHER AND ITS         RESPECTIVE TIME TAKEN IN MINUTES.       TABLE ADAPTED FROM AYAVOO ET AL. (2006), TABLE 3                                                                                                                                                           |

| TABLE 6-3 THE RESULTS FOR EFFORT (IN MINUTES) FOR CASE STUDY 6.       81                                                                                                                                                                                                                                                                                  |

| TABLE 6-4 PERCENTAGE OF THE EFFORT INVOLVED FOR THE DIFFERENT DEVELOPMENT APPROACHES FOR         CASE STUDY 6                                                                                                                                                                                                                                             |

| TABLE 7-1 THE CONTROL DELAY (IN MS) RECORDED BY ALL THE GROUPS IN CASE STUDY 7                                                                                                                                                                                                                                                                            |

| TABLE 8-1 THE GQM APPROACH USED IN CASE STUDY 8.    108                                                                                                                                                                                                                                                                                                   |

| TABLE 8-2 THE MEAN RESULTS FOR CASE STUDY 8.    112                                                                                                                                                                                                                                                                                                       |

| TABLE 8-3 THE SYNCHRONISED RESULTS OF THE EFFORT AND CHANGES MADE FOR CASE STUDY 8-I.         113                                                                                                                                                                                                                                                         |

| TABLE 8-4 THE RESULTS (IN TOTAL) FOR EFFORT, RELIABILITY AND MODULARITY OF THE PATTERNS IN CASE         STUDY 8-1.                                                                                                                                                                                                                                        |

| TABLE 8-5 THE SYNCHRONISED RESULTS FOR EFFORT AND CHANGES MADE FOR CASE STUDY 8-II.       115                                                                                                                                                                                                                                                             |

| TABLE 8-6 THE RESULTS (IN TOTAL) FOR EFFORT, RELIABILITY AND MODULARITY OF THE PATTERNS IN CASE         STUDY 8-II. TABLE ADAPTED FROM PONT <i>ET AL.</i> (SUBMITTED), TABLE 3                                                                                                                                                                            |

# LIST OF PUBLICATIONS

A number of papers were published during the course of the work described in this thesis. These are listed below (in reverse chronological order). Please note that the contents of some of these papers have been adapted for presentation in this thesis: where applicable, a footnote at the beginning of a chapter indicates that material from one or more papers has been included. For those papers with contents that have not been included in this thesis, a copy of the paper itself is included in the appendices.

#### **Directly-related publications**

- Ayavoo, D., Pont, M. J. and Parker, S. (in preparation) "Developing reliable embedded systems: Does a 'simulation first' approach improve software quality?".

- Ayavoo, D., Pont, M. J. and Parker, S. (submitted 29 August 2006) "Comparing different techniques for developing software for mechatronic systems: A low-cost empirical methodology". IEEE/ASME Transactions on Mechatronics.

- Pont, M. J., Mwelwa, C., Bonthonneau, L., Ayavoo, D., Kurian, S. and Ward, D. (submitted 10 August 2006) "Pattern-based development of time-triggered embedded systems using software tools: Challenges and solutions". Journal of Systems and Software.

- Ayavoo, D., Pont, M.J. and Parker, S. (2006) "Does a 'simulation first' approach reduce the effort involved in the development of distributed embedded control systems?".

Proceedings of the 6th UKACC International Control Conference, Glasgow, Scotland, 2006.

- Ayavoo, D., Pont, M.J. and Parker, S. (2005a) "Observing the development of a reliable embedded system". In Vardanega, T. and Wellings, A. (Eds.) "Proceedings of the 10th Ada-Europe International Conference on Reliable Software Technologies, York, UK, June 20-24 2005", p. 167-179. Lecture Notes in Computer Science, Vol. 3555. Published by Springer-Verlag [ISBN: 3-540-26286-5]. (A copy of this paper is included in Appendix-A)

- Ayavoo, D., Pont, M.J. and Parker, S. (2004) "Using simulation to support the design of distributed embedded control systems: A case study". In: Koelmans, A., Bystrov, A. and Pont, M.J. (Eds.) "Proceedings of the 1st UK Embedded Forum 2004 (Birmingham, UK, October 2004)", p. 54-65. Published by University of Newcastle upon Tyne [ISBN: 0-7017-0180-3].

#### **Associated publications**

- Ayavoo, D., Pont, M.J., Short, M. and Parker, S. (accepted) "Two novel shared-clock scheduling algorithms for use with CAN-based distributed systems". Microprocessors and Microsystems. (Accepted for publication subject to minor revisions. A copy of this paper is included in Appendix-B)

- Ayavoo, D., Pont, M.J., Short, M. and Parker, S. (2005b) "Two novel shared-clock scheduling algorithms for use with CAN-based distributed systems". In: Koelmans, A., Bystrov, A., Pont, M.J., Ong, R. and Brown, A. (Eds.), Proceedings of the Second UK Embedded Forum (Birmingham, UK, October 2005), p. 246-261. Published by University of Newcastle upon Tyne [ISBN: 0-7017-0191-9].

- Ayavoo, D., Pont, M.J., Fang, J., Short, M. and Parker, S. (2005c) "A 'hardware-in-the-loop' testbed representing the operation of a cruise-control system in a passenger car". In: Koelmans, A., Bystrov, A., Pont, M.J., Ong, R. and Brown, A. (Eds.), Proceedings of the Second UK Embedded Forum (Birmingham, UK, October 2005), p. 60-90. Published by University of Newcastle upon Tyne [ISBN: 0-7017-0191-9]. (A copy of this paper is included in Appendix-C)

# List of Abbreviations, Symbols and Units

# Abbreviations

| Appleviations |                                                     |

|---------------|-----------------------------------------------------|

| ACCS          | Adaptive Cruise-Control System                      |

| ADC           | Analogue to Digital Converter                       |

| ASIC          | Application Specific Integrated Circuit             |

| CA            | Controller/Actuator                                 |

| CAN           | Controller Area Network                             |

| CASE          | Computer Aided Software Engineering                 |

| CCS           | Cruise-Control System                               |

| CSMA/CA       | Carrier Sense Multiple Access / Collision Avoidance |

| DAC           | Digital to Analogue Converter                       |

| DSP           | Digital Signal Processor                            |

| DVD           | Digital Versatile Disc                              |

| ESL           | Embedded Systems Laboratory                         |

| FPGA          | Field Programmable Gate Array                       |

| GQM           | Goal Question Metrics                               |

| HIL           | Hardware-in-the-Loop                                |

| HW            | Hardware                                            |

| I/O           | Input/Output                                        |

| IMP           | Implementation                                      |

| kbps          | kilo bits per second                                |

| LĊD           | Liquid Crystal Display                              |

| LED           | Light Emitting Diode                                |

| LIN           | Local Interconnect Network                          |

| LOC           | Lines of (Source) Code                              |

| LQR           | Linear Quadratic Regulator                          |

| Mbps          | Mega bits per second                                |

| 0-0           | Object-Oriented                                     |

| PDA           | Personal Digital Assistant                          |

| PID           | Proportional, Integral and Derivative               |

| PIE           | Pattern Implementation Example                      |

| PTTES         | Patterns for Time-Triggered Embedded Systems        |

| PWM           | Pulse Width Modulation                              |

| SCC           | Shared-Clock CAN                                    |

| SGM           | Small Group Methodology                             |

| SIM           | Simulation                                          |

| SW            | Software                                            |

| TDMA          | Time Division Multiple Access                       |

| TTCAN         | Time-Triggered Controller Area Network              |

| ТТР           | Time-Triggered Protocol                             |

| TTP/C         | Time-Triggered Protocol, Class C                    |

| TT-Plus       | TrueTime-Plus                                       |

| UML           | Unified Modelling Language                          |

| VAN           | Vehical Area Network                                |

|               |                                                     |

### Symbols

| •              |                        |

|----------------|------------------------|

| а              | Acceleration           |

| Fr             | Frictional coefficient |

| т              | Mass                   |

| $v_f$          | Final speed            |

| v <sub>i</sub> | Initial speed          |

| $\Delta x$     | Displacement           |

| $\theta$       | Throttle setting       |

| τ              | Engine torque          |

|                |                        |

# Units

| Units |                 |

|-------|-----------------|

| m/s   | Metres / Second |

| ms    | Millisecond     |

| S     | Second          |

| μs    | Microsecond     |

|       |                 |

# 1. Introduction

In this introductory chapter, an overview of the work undertaken in this thesis is presented and the importance of this area is discussed.<sup>1</sup>

### **1.1 Introduction**

Most branches of engineering have a long history associated with them. For instance, the study of electrical engineering can be dated back to the invention of the electric motor by Michael Faraday in 1821 (Faraday, 2004), while James Watt is largely recognised for his seminal contributions to control engineering with the development of the flyball governor in the 1760s (Marsden, 2004). It is possible that the practice of civil engineering may have the longest history of all, dating back to the building of the Egyptian pyramids. Certainly, the Institution of Civil Engineers was founded in the UK in 1818 and is the oldest professional engineering institution in the world (ICE, 2006).

For the software engineer, a different situation applies. Although Charles Babbage began work on his 'Analytical Engine' around 1833 (Babbage, 1888), it was not until 1965 that the first mass-produced mini computer, the PDP-8, was launched (Jones, 2004). Intel followed suit with the release of the first microprocessor, the Intel 4004, only in 1971 (Wilson, 2001). As a result of the late introduction of small programmable computer systems, the field of software engineering lacks the rigorous theoretical foundation which marks out most branches of the engineering profession. This situation might not matter if software development was a niche occupation: however, the development of software-based systems lies at the heart of many business and technical activities (Storey, 1996; Lewis, 2001).

The focus of this thesis is on the development of reliable software for embedded systems. Embedded systems are special-purpose computers that combine hardware and software and are mounted on compact electronic circuit boards that are used inside a particular device (Sachitanand, 2002). Very often, such systems interact with the real world through input/output devices such as push-button switches, potentiometers, LCD panels and LEDs.

<sup>&</sup>lt;sup>1</sup> Parts of this chapter have previously been published in Ayavoo *et al.* (2004) and Ayavoo *et al.* (2006).

Embedded systems may include microcontrollers, microprocessors, DSPs, FPGAs and/or ASICs to perform the core computation.

Embedded processors can be found in many day-to-day applications such as digital cameras, Personal Digital Assistants (PDAs), palm top computers, DVD players and mobile phones (Chouliaras *et al.*, 2005). In addition to these "non-critical" systems, embedded processors are also used in safety-critical applications such as automotive, aerospace, defence and medical systems (Storey, 1996). The use of embedded processors in such applications is very attractive as it can greatly improve the functionality of a particular product at very low cost (Pont, 2001; Sachitanand, 2002). Over the years, many industrial firms (such as Intel, Infineon, Philips, Atmel, Altera, Xilinx, Texas Instruments) have been actively producing a range of different embedded processors to match the growing needs and demand of the modern technology. Overall, embedded processors are poised to revolutionise many industrial sectors and consumer products by making various systems more "intelligent".

#### 1.2 Description of the problem

With the rapid growth of technology, the development of huge and complex embedded systems is becoming increasingly difficult; especially where system safety and reliability is crucial. This section describes the difficulties involved in detail.

#### 1.2.1 Distributed embedded control systems in the automotive sector

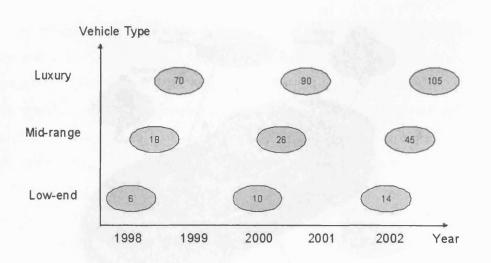

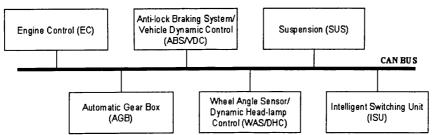

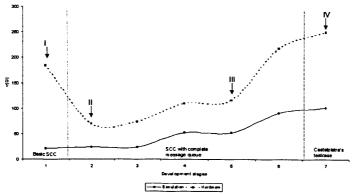

The focus of the work presented in this thesis is on the development of reliable embedded systems, particularly for automotive applications. Here, embedded processors are becoming ubiquitous (Maier *et al.*, 2002) and are used to perform a variety of safety-related functions in the vehicle such as automatic transmission, anti-lock braking systems and engine control. The number of embedded processors used in a vehicle has also been steadily increasing over the past few years (see Figure 1-1), and it is expected that this trend will continue over the next few years, as the complexity and functionality of the system increases (Lanfear *et al.*, 2006).

Figure 1-1 Microcontroller implementation growth in automobiles. Redrawn from data in Bannatyne (2003), Figure 1.

It is also expected that an increasing number of road vehicles will soon contain sophisticated distributed embedded control systems, consisting of a number of microcontrollers linked by one or more computer networks (Leen *et al.*, 1999): crucially, these systems will have no mechanical backup. As with similar distributed embedded control systems in other sectors (including aerospace, medicine, manufacturing and defence), these embedded automotive designs will be highly complex, and will have a central role in safety.

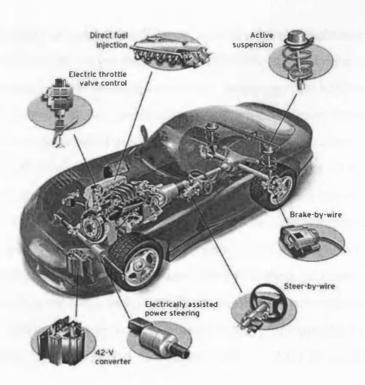

This cutting edge technology, which is also known as X-by-Wire<sup>2</sup> systems (Ellims *et al.*, 2002; Fredriksson, 2002; Koopman, 2002; Nossal and Lang, 2002), can be argued to have been inspired by the success of Fly-by-Wire systems adopted in the aerospace industry (Brière *et al.*, 1995; Schmitt *et al.*, 1998). The 'X' in X-by-Wire represents the basis of any safety-related application, such as steering, braking, power train, throttle or suspension control systems (see Figure 1-2). It is expected that X-by-Wire systems will assist the driver in different situations and make it safer for all road-users (Bretz, 2001; Koopman, 2002).

<sup>&</sup>lt;sup>2</sup> Please note that the term X-by-Wire is used in the remainder of this thesis to represent any distributed embedded control systems.

Figure 1-2 An illustration of an X-by-Wire system in a car from Bretz (2001), Figure 1. Copyright IEEE, reproduced with permission.

#### 1.2.2 Why is the development of X-by-Wire systems difficult?

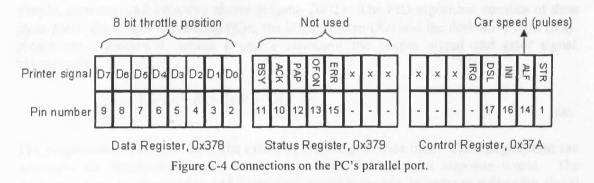

The designers of X-by-Wire systems, particularly for those in the automotive industry, face the challenge that the resulting systems must operate very reliably, and - at the same time - have minimal maintenance requirements and a low purchase price (Kopetz, 1995; Schoitsch, 2003). As a consequence of the market's demand for lower cost, the X-by-Wire systems often have to operate within severe resource constraints such as limited CPU speed, memory constrictions, minimal hardware peripherals and restricted network bandwidth.