## DESIGN PATTERNS TO SUPPORT THE MIGRATION BETWEEN

## EVENT-TRIGGERED AND TIME-TRIGGERED SOFTWARE

## ARCHITECTURES

Thesis submitted for the degree of Doctor of Philosophy at the University of Leicester

by Farha Lakhani Embedded Systems Research Group Department of Engineering University of Leicester Leicester, UK

June 2013

#### Farha Lakhani

# Design patterns to support the migration between event-triggered and time-triggered software architectures

#### Abstract

There are two main architectures used to develop software for modern embedded systems: these can be labelled as "event-triggered" (ET) and "timetriggered" (TT). This thesis is concerned with the issues involved in migration between these two architectures.

Although TT architectures are widely used in safety-critical applications (for example, in aerospace and medical systems) they are less familiar to developers of mainstream embedded systems. The work in this thesis began from the premise that – for a broad class of systems that have been implemented using an ET architecture – migration to a TT architecture would improve reliability.

It may be tempting to assume that conversion between ET and TT designs will simply involve converting all event-handling software routines into periodic activities. However, the required changes to the software architecture are, in many cases rather more profound. The main contribution of the work presented in this thesis is to identify ways in which the significant effort involved in migrating between existing ET architectures and "equivalent" (and effective) TT architectures could be reduced. The research has taken an innovative step in this regard by introducing the use of 'Design patterns' for this purpose for the first time.

This thesis describes the development, experimental testing and preliminary assessment of a novel set of design patterns. The thesis goes on to evaluate the effectiveness of some of the key patterns in the development of some representative systems. The pattern evaluation process involved both controlled laboratory experiments on real-time applications, and comprehensive feedback from experts in industry.

The results presented in this thesis suggest that pattern-based approaches have the potential to simplify the migration process between ET and TT architectures.

The thesis concludes by presenting suggestions for future work in this important area.

#### Acknowledgements

This thesis is an accumulation of three years of work and this journey would not have been possible for me without the support from a number of people I met during this period.

Firstly, my research supervisor Professor Michael J. Pont deserves the highest gratitude for providing his guidance, feedback and for his encouragement throughout my research. I am highly indebted to him for providing me the opportunity to present and defend my work at various events during the research. Apart from technical guidance there was much for me to learn from his professionalism, passion and zeal in his inspirational work which I will always remember and appreciate.

Next, my heart-felt thanks to Dr. Kevin Byron for providing me his kind help and support in the early stages of the research which enabled my research flight take off at the right time and to be a pleasant experience. Also thanks are due to PG tutor Dr. Fernando Schlindwein for his help and support.

I feel myself fortunate for having a highly competent and professional team of people working around me during the course of my research. I take all these people as stars lighting up the path and making the walk easier for me. I am thankful to Dr. Anjali Das, Dr. Ayman Gendy, Azura, Dr. Devaraj Ayavoo, Huiyan Wang, Dr. Imran Sheikh, Ioannis Kyriakopoulos, Dr. Kam Chan, Dr. Keith Athaide, Mohammad Aamir, Dr. Musharraf Hanif, Peter Vidler, Dr. Susan Kurian, Syed Aley Imran Rizvi, and Dr. Zemian Hughes.

A special thanks to Georgy Holden, Hooriyah Begg, Dr. Keith Athaide, Dr. Kevin Byron and Dr. Susan Kurian for their help in proof reading my thesis and for giving valuable feedback, and to Dr. Keith Athaide and Dr. Zemian Hughes for helping in experimental work during the research.

I can never forget my lovely parents to whom I am always indebted for everything they gave me and did for me. Compliments are due to my late father for providing me support and inspiration throughout his life that motivates me to achieve the best even today. Thanks to my mum for her countless prayers for my success. I am also grateful to every member in my family.

Thanks to my enduring friend Anila Soomro for all her love and support during the last three years and for lifting up my morale from abroad.

Also, I would like to take this opportunity to thank my funding body - the Higher Education Commission of Pakistan government and Bahria University.

Dedicated to my loving mother and to my very dear departed father Mushtaq Ahmed Lakhani

# TABLE OF CONTENTS

| TABLE             | OF CONTENTS                                                         | I     |  |

|-------------------|---------------------------------------------------------------------|-------|--|

| LIST OF FIGURESIV |                                                                     |       |  |

| LIST O            | F TABLES                                                            | .VIII |  |

| LIST O            | F PUBLICATIONS                                                      | Х     |  |

| LIST O            | F ABBREVIATIONS, SYMBOLS AND UNITS                                  | XII   |  |

| PART              | A: INTRODUCTION                                                     | 1     |  |

| СНАРТ             | ER 1. INTRODUCTION                                                  | 2     |  |

| 1.1.              | Introduction to the problem                                         | 2     |  |

| 1.2.              | Description of the problem addressed in this thesis                 |       |  |

| 1.3.              | Research contributions                                              | 8     |  |

| 1.4.              | Outline of the thesis                                               | 9     |  |

| 1.5.              | Conclusions                                                         | 12    |  |

| СНАРТ             | ER 2. MOTIVATING EXAMPLES                                           | 13    |  |

| 2.1.              | Introduction                                                        | 13    |  |

| 2.2.              | The F-18 Mission Computer                                           | 13    |  |

| 2.3.              | Migration towards time-triggered image acquisition                  | 16    |  |

| 2.4.              | Sony® cell processor                                                | 18    |  |

| 2.5.              | Discussion                                                          | 19    |  |

| 2.6.              | Conclusion                                                          | 21    |  |

| СНАРТ             | ER 3. METHODOLOGY                                                   | 23    |  |

| 3.1.              | Introduction                                                        | 23    |  |

| 3.2.              | General approach to the investigation                               | 23    |  |

| 3.3.              | Formulation of the research problem                                 | 25    |  |

| 3.4.              | Development of hypothesis and choosing the appropriate methodology. | 27    |  |

| 3.5.              | Implementation of the chosen methodology                            | 34    |  |

| 3.6.              | Evaluation                                                          | 34    |  |

| 3.7.              | Conclusion                                                          | 36    |  |

| PART              | B: LITERATURE REVIEW                                                | 38    |  |

| CHAPT<br>ARCHI    | ER 4. EVENT-TRIGGERED AND TIME-TRIGGEI                              |       |  |

| 4.1.              | Introduction                                                        | 39    |  |

| 4.2.              | Taxonomy of scheduling techniques                                   | 40    |  |

| 4.3.              | Software architectures for embedded applications                    | 50    |  |

| 4.4.              | Event-triggered versus time-triggered architectures                 | 57    |  |

| 4.5.              | Discussion                                                          | 59    |  |

| 4.6.              | Conclusions                                                         | 66    |  |

|       | ER 5. MIGRATION OF ARCHITECTURES IN CATIONS           |         |

|-------|-------------------------------------------------------|---------|

| 5.1.  | Introduction                                          | 68      |

| 5.2.  | Related terminology                                   | 69      |

| 5.3.  | The need for migration in embedded software           | 71      |

| 5.4.  | Dependencies between components in embedded software. | 74      |

| 5.5.  | Existing techniques in the literature                 | 77      |

| 5.6.  | Conclusions                                           |         |

| СНАРТ | ER 6. DESIGN PATTERNS                                 |         |

| 6.1.  | Introduction                                          |         |

| 6.2.  | Design patterns in architecture                       |         |

| 6.3.  | Design patterns beyond architecture                   |         |

| 6.4.  | Patterns and embedded software development            |         |

| 6.5.  | Broader aspects of patterns                           |         |

| 6.6.  | Pattern forms                                         |         |

| 6.7.  | Pattern languages                                     | 97      |

| 6.8.  | Pattern mining and refinement                         |         |

| 6.9.  | Inadequacies of patterns                              | 102     |

| 6.10. | Conclusions                                           | 104     |

| PART  | C: DEVELOPMENT OF PATTERNS FOR MIGRATION.             |         |

| СНАРТ | ER 7. DERIVATION OF "PATTERNS FOR MIGRATI             | ON" 106 |

| 7.1.  | Introduction                                          | 106     |

| 7.2.  | Rationale for patterns to support migration           | 106     |

| 7.3.  | Choosing the appropriate architecture                 | 109     |

| 7.4.  | Transforming an ET design to a TT design              | 110     |

| 7.5.  | Choosing the appropriate TT architecture              | 111     |

| 7.6.  | Handling events in TT designs                         | 112     |

| 7.7.  | Handling problems with the co-operative design        | 113     |

| 7.8.  | Handling problems with the pre-emptive designs        | 116     |

| 7.9.  | Designing tasks for a TT design                       |         |

| 7.10. | Achieving a 'Balanced' TT design                      | 117     |

| 7.11. | Monitoring the TT design                              |         |

| 7.12. | Conclusion                                            |         |

| СНАРТ |                                                       |         |

| 8.1.  | Introduction                                          | 121     |

| 8.2.  | Pattern categories in the PMES collection             | 122     |

| 8.3.  | PMES – towards a pattern language for migration       | 123     |

| 8.4.  | Patterns for migration                                | 127     |

| 8.5.  | Conclusions                                           |         |

| СНАРТ                                                      | TER 9. APPLYING THE PATTERNS TO REAL APPLICATIONS           | 5 149        |

|------------------------------------------------------------|-------------------------------------------------------------|--------------|

| 9.1.                                                       | Introduction                                                | 149          |

| 9.2.                                                       | Hardware specifications and methodology                     | 150          |

| 9.3.                                                       | Example 1: Data Acquisition System                          | 155          |

| 9.4.                                                       | Example 2: FFT/ADC framework                                | 170          |

| 9.5.                                                       | Discussion                                                  | 179          |

| 9.6.                                                       | Conclusions                                                 | 180          |

| СНАРТ                                                      | TER 10. ASSESSING THE PATTERNS: EMPIRICAL STUDIES.          | 181          |

| 10.1.                                                      | Introduction                                                | 181          |

| 10.2.                                                      | Evaluation of design patterns – an overview                 | 182          |

| 10.3.                                                      | Related work                                                | 184          |

| 10.4.                                                      | Preliminary evaluation of the PMES collection               | 192          |

| 10.5.                                                      | Empirical studies for the evaluation of the PMES collection | 194          |

| 10.6.                                                      | Experiment planning                                         | 196          |

| 10.7.                                                      | Experiment 1: Patterns for experienced developers           | 200          |

| 10.8.                                                      |                                                             |              |

| 10.9.                                                      | Discussion                                                  | 221          |

| 10.10                                                      | ). Conclusions                                              | 226          |

| CHAPT                                                      | FER 11. ASSESSING THE PATTERNS: INDUSTRY FEEDBACH           | <b>〈</b> 227 |

| 11.1.                                                      | Introduction                                                | 227          |

| 11.2.                                                      | PMES usability in the industrial context                    | 228          |

| 11.3.                                                      | Aims of the evaluation                                      | 231          |

| 11.4.                                                      | Practical constraints involved with industrial evaluation   | 231          |

| 11.5.                                                      | Methodology                                                 | 232          |

| 11.6.                                                      | Results                                                     | 240          |

| 11.7.                                                      | Discussion                                                  | 260          |

| 11.8.                                                      | Conclusion                                                  | 263          |

| CHAPT                                                      | TER 12. CONCLUSIONS AND FUTURE WORK                         | 264          |

| 12.1.                                                      | Reasons and motivation for the thesis work                  | 264          |

| 12.2.                                                      | A review of the contributions                               | 266          |

| 12.3.                                                      | Research implications and shortcomings                      | 269          |

| 12.4.                                                      | Scope for future work                                       | 271          |

| 12.5.                                                      | Final conclusions                                           | 273          |

| PART                                                       | D: APPENDICES                                               | 275          |

| APPEN                                                      | IDIX A: PATTERN FORMS                                       | 276          |

| APPEN                                                      | IDIX B: SPECIFICATIONS OF THE PMES COLLECTION               | 281          |

| APPEN                                                      | IDIX C: DOCUMENTS RELATED TO EMPIRICAL STUDIES              | 328          |

| APPENDIX D: DOCUMENTS RELATED TO INDUSTRIAL EVALUATION 344 |                                                             |              |

| PART E: REFERENCES                                         |                                                             |              |

# LIST OF FIGURES

| Figure 1-1 Embedded systems market 2009-2015 (Source: BCC research)                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-1 Model of F-18 MC [adapted from (Shepard and Gagne, 1990)]14                                                                                |

| Figure 2-2 Layout of the vision-based distributed embedded control application [Adapted from (Kubinger and Humenberger, 2004)]17                      |

| Figure 3-1 Illustrating the different steps taken during the main phases of the research process                                                      |

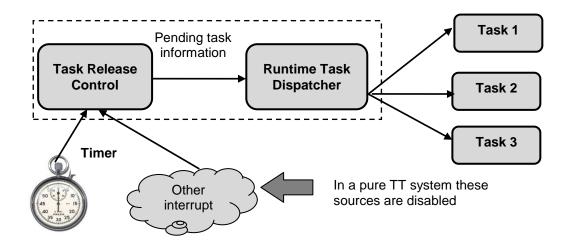

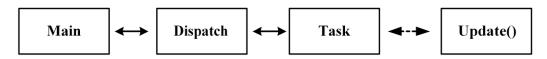

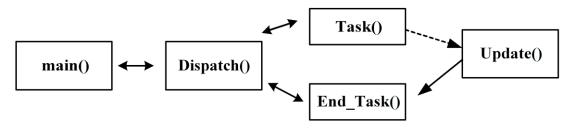

| Figure 4-1 An illustration of scheduler functions41                                                                                                   |

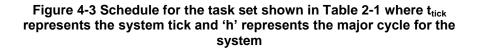

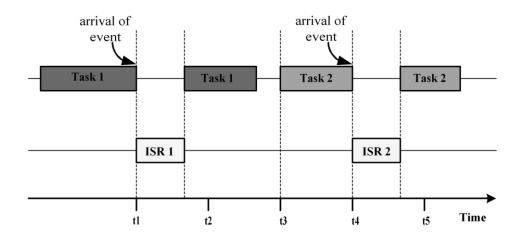

| Figure 4-2 Illustrating the execution of co-operative tasks where one waits until the other finish execution                                          |

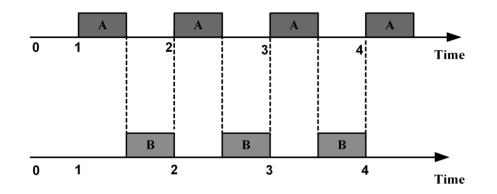

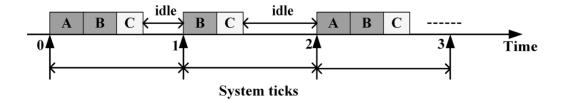

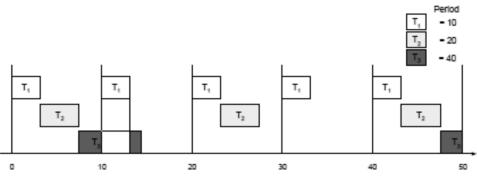

| Figure 4-3 Schedule for the task set shown in Table 2-1 where $t_{tick}$ represents the system tick and 'h' represents the major cycle for the system |

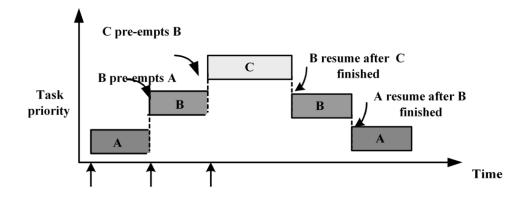

| Figure 4-4 Illustrating pre-emptive tasks where a higher priority task pre-empts the lower priority task upon its arrival                             |

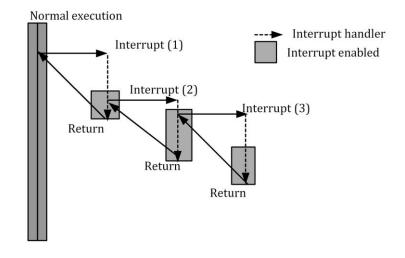

| Figure 4-5 Illustrating the interrupt handling mechanism in an embedded application [Adapted from (Pont, 2001)]                                       |

| Figure 4-6 Illustrating the process of task switching as various interrupts occur in a nested interrupt based system                                  |

| Figure 4-7 TTC schedule for the task set shown in Table 4-255                                                                                         |

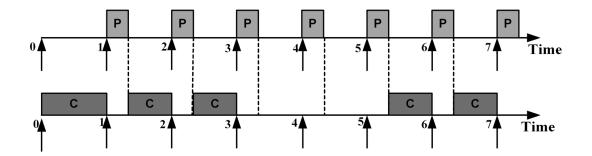

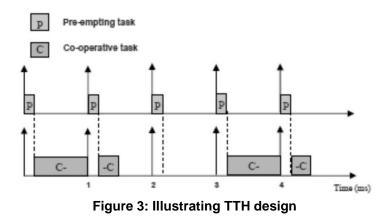

| Figure 4-8 Illustrating the operation of a TTH scheduler56                                                                                            |

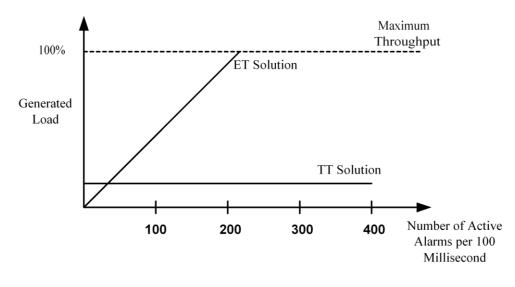

| Figure 4-9 Load generated by ET and TT solutions of the alarm monitoring system [adapted from (Kopetz, 1997)]                                         |

| Figure 5-1 An illustration of dependencies between different software components of a simple embedded application                                     |

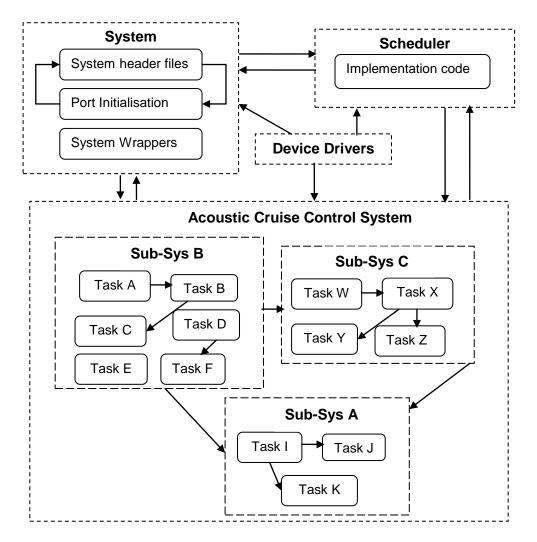

| Figure 5-2 Dependency between different components in a complex control system                                                                        |

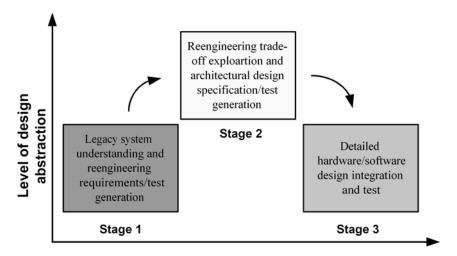

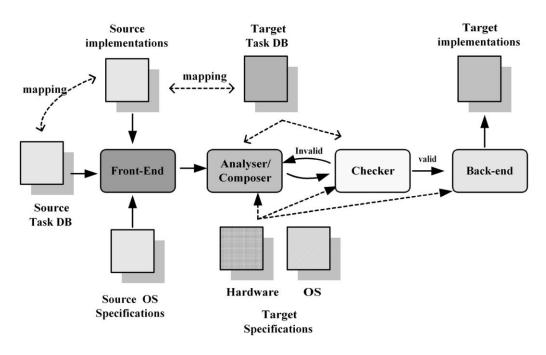

| Figure 5-3 Three stage process for re-engineering legacy embedded applications [adapted from (Madisetti, Jung et al, 1999)]                           |

| Figure 5-4 Design of the RTSC [Adapted from (Scheler and Schroder-Preikschat, 2010)]79                                                                |

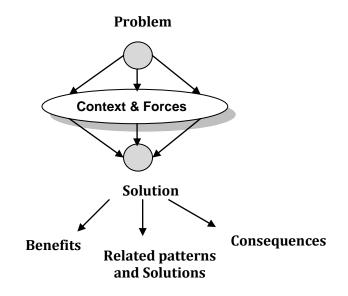

| Figure 6-1 Illustrating the concept of a design pattern92                                                                                             |

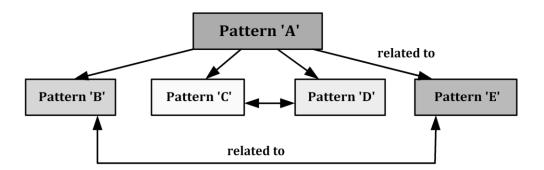

| Figure 6-2 Illustrating an example structure of a pattern language97                                                                                  |

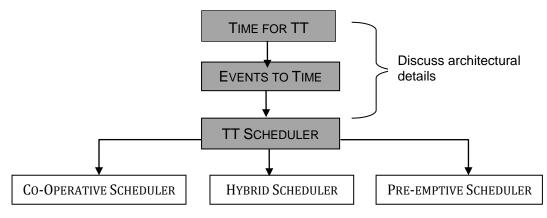

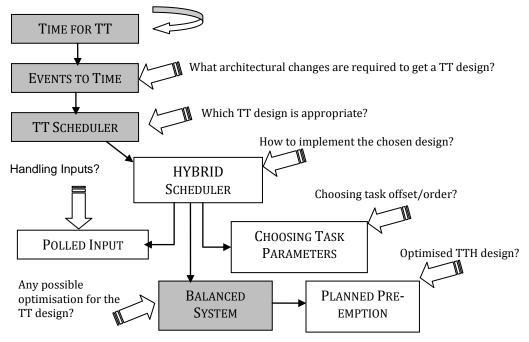

| Figure 7-1 Illustrating the sequence of following patterns from the initial decision of migration to choosing an appropriate TT design                |

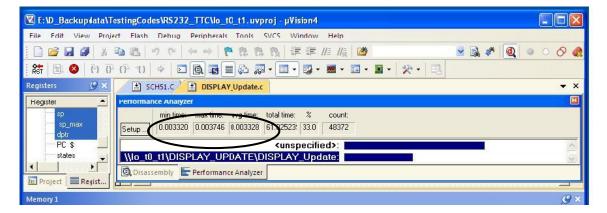

| Figure 7-2 Performance Analyzer in the Keil simulator showing the execution time of the Display_Update() task = 47 ms with printf() function                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7-3 Performance Analyzer in the Keil simulator showing the execution time of the Display_Update task = 3ms using Buffered output technique                         |

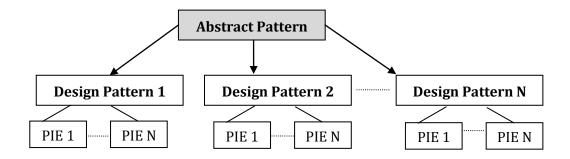

| Figure 8-1 One-to-many relationship between abstract pattern, design patterns and PIEs 122                                                                                |

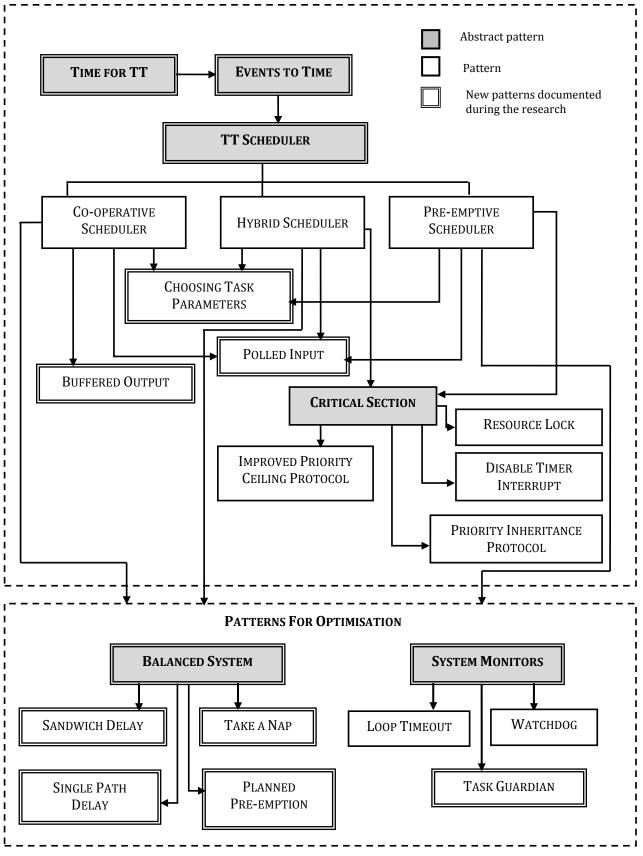

| Figure 8-2 Association map for the PMES language125                                                                                                                       |

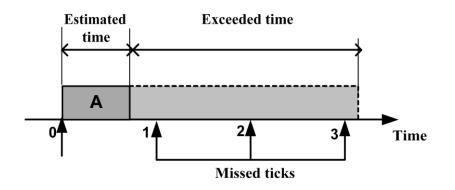

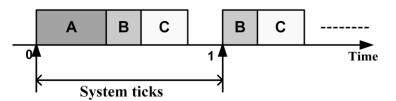

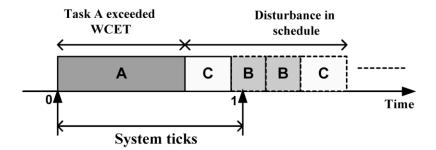

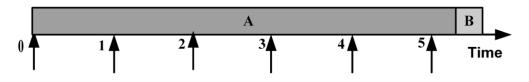

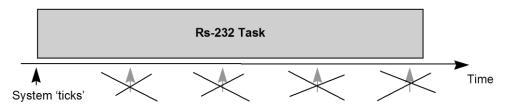

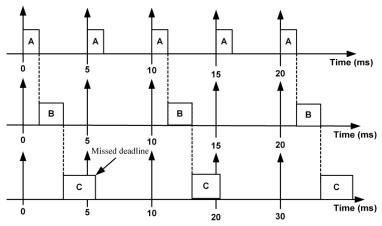

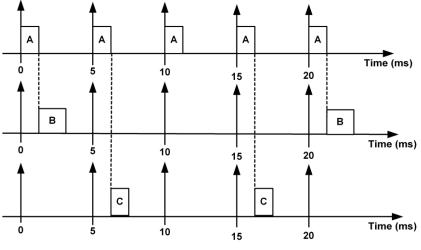

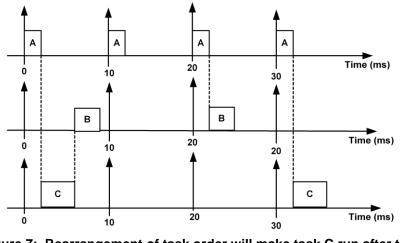

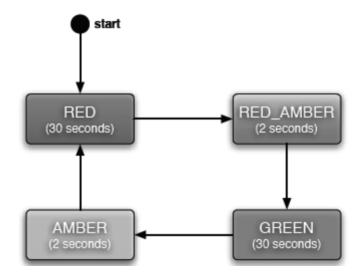

| Figure 8-3 Illustrating the problem of a long task in TTC environment                                                                                                     |

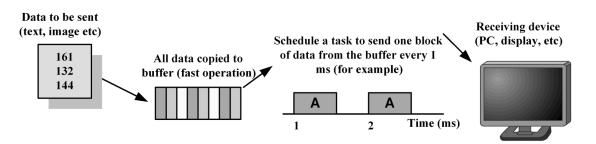

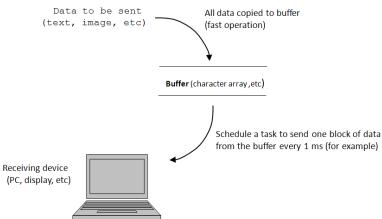

| Figure 8-4 An overview of the Buffered Output architecture                                                                                                                |

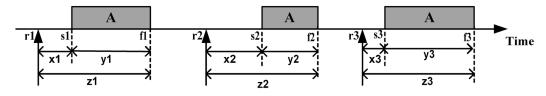

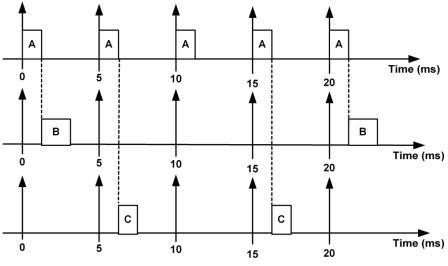

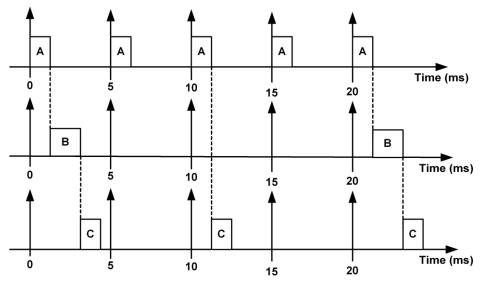

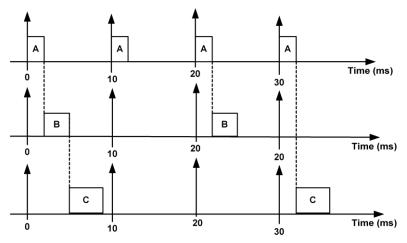

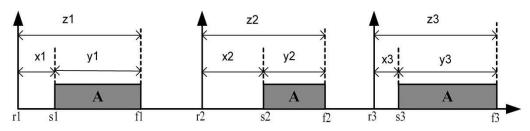

| Figure 8-5 Illustrating the presence of release, execution and finishing jitter in different instances of a task                                                          |

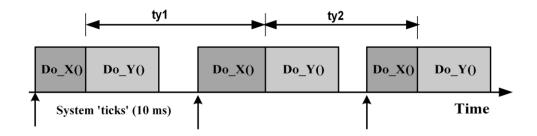

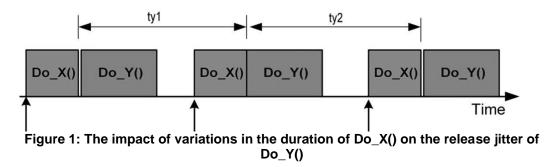

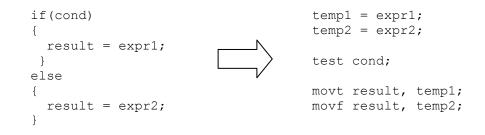

| Figure 8-6 Impact of variations in the duration of task Do_X() on the release jitter of task Do_Y()                                                                       |

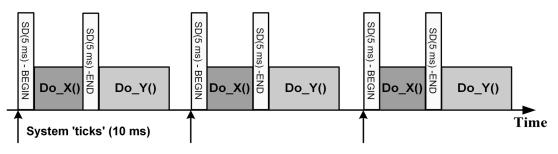

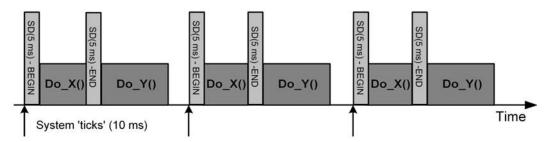

| Figure 8-7 Illustrating the use of the Sandwich Delay technique137                                                                                                        |

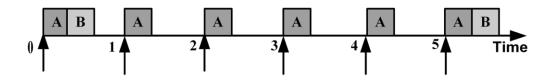

| Figure 8-8 Three tasks with same release time scheduled to run in a tick                                                                                                  |

| Figure 8-9 Illustrating the change in system behaviour if the execution time of task A takes longer than expected                                                         |

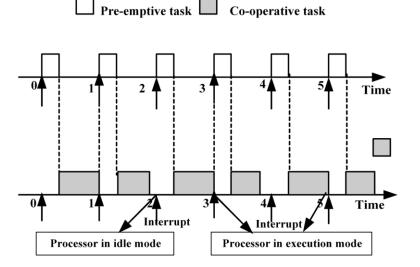

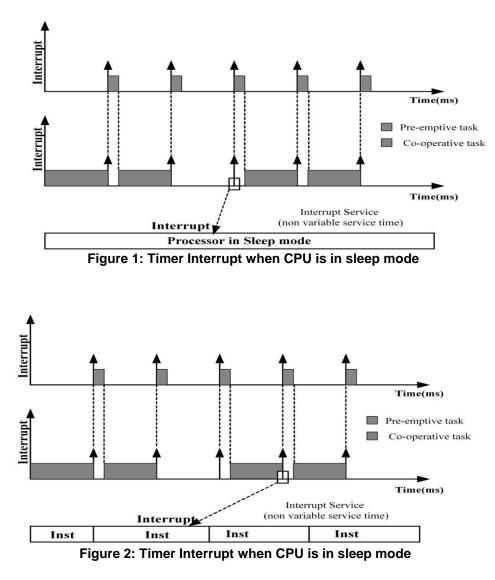

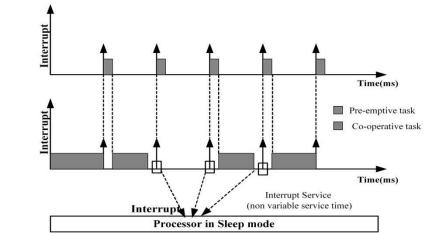

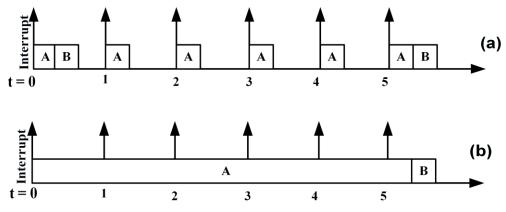

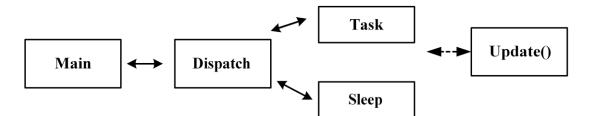

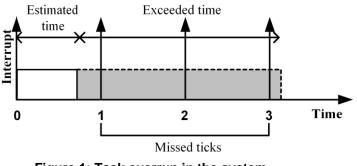

| Figure 8-10 Illustrating the Occurrences of timer interrupts when processor is in different modes                                                                         |

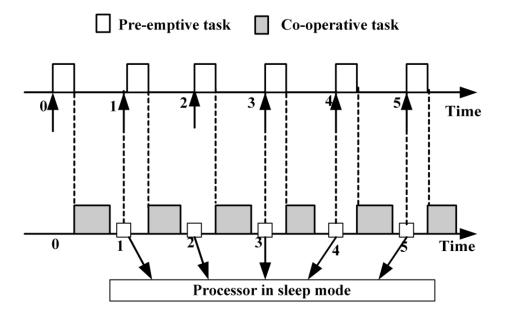

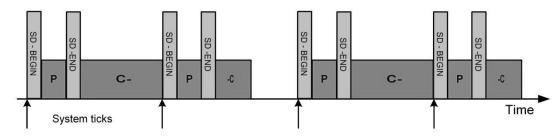

| Figure 8-11 Illustrating the operation of 'Planned Pre-emption' where processor is put to sleep mode just before the system tick occurs                                   |

| Figure 8-12 Illustrating a TTC based system running in normal conditions147                                                                                               |

| Figure 8-13 Illustrating the TTC system when task A overruns                                                                                                              |

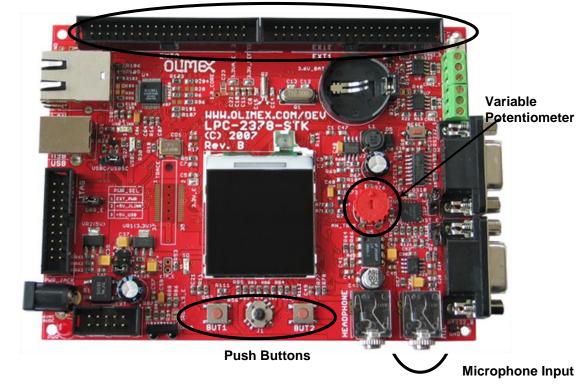

| Figure 9-1 Prototype board for ARM 7 LPC2378STK [courtesy: (OLIMEX2378, 2012) ] 151                                                                                       |

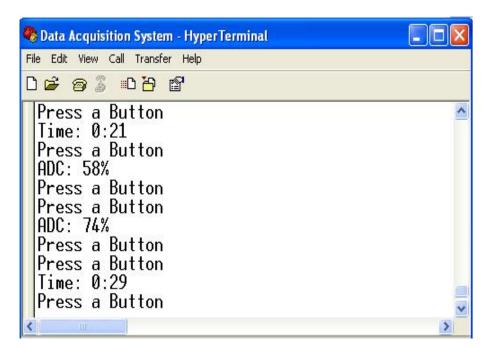

| Figure 9-2 A sample output shown using hyper terminal for the DAQ system156                                                                                               |

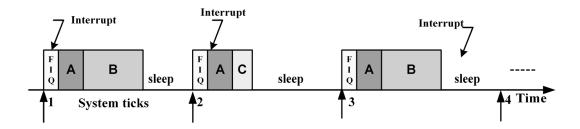

| Figure 9-3 Illustrating possible interrupt arrivals during task execution159                                                                                              |

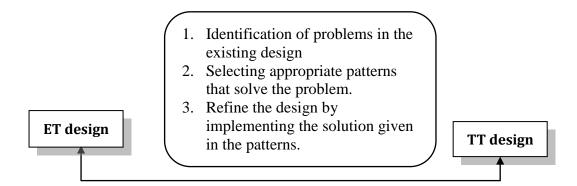

| Figure 9-4 Illustrating the process of applying patterns for the conversion of ET design to TT design                                                                     |

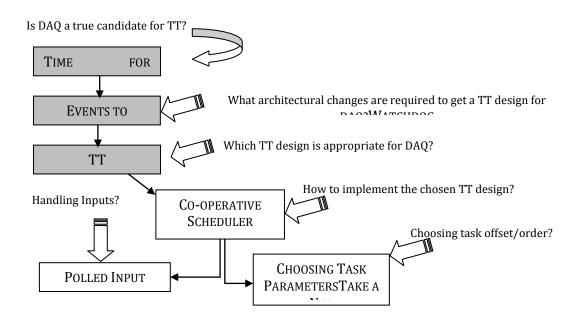

| Figure 9-5 An excerpt from the pattern 'TIME FOR TT?' highlighted sections showing how the pattern is applicable in the context of DAQ for migration from ET to TT design |

| Figure 9-6 An excerpt from pattern 'EVENTS TO TIME' with highlighted sections indicating the relevance of the pattern in the context of getting a TT design for the DAQ   |

| Figure 9-7 A possible sequence of patterns to follow in achieving a TT design for the DAQ system                                                                          |

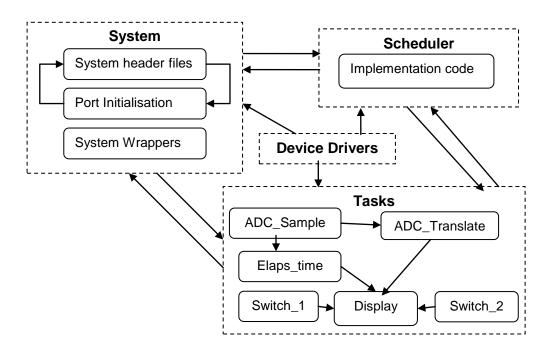

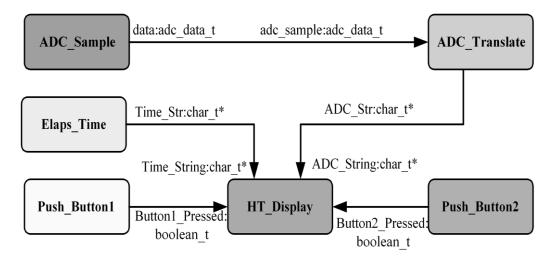

| Figure 9-8 High level task representation of TT design for DAQ system                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

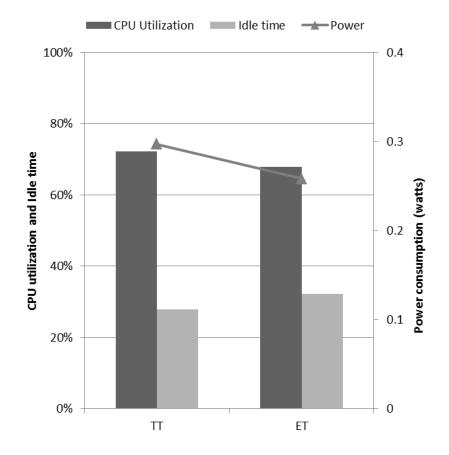

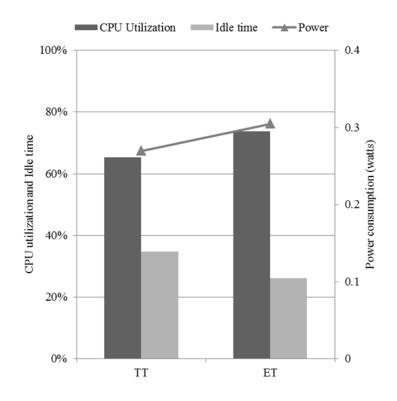

| Figure 9-9 Comparison of CPU utilization, idle time and power consumption for ET and TT design for DAQ system                                                    |

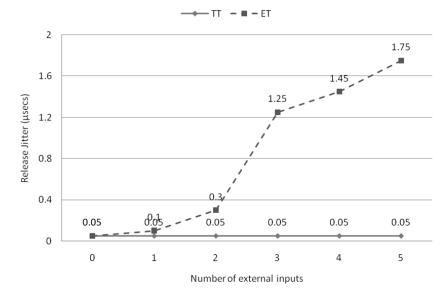

| Figure 9-10 Release jitter in the data sampling task of ET and TT designs for DAQ system 168                                                                     |

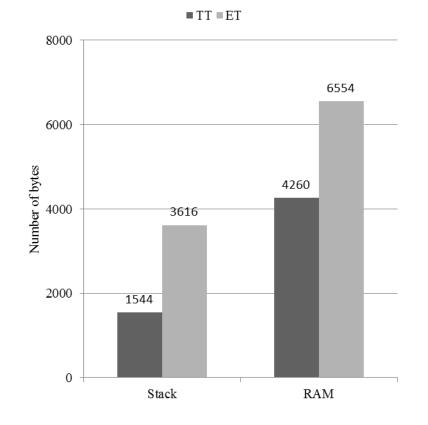

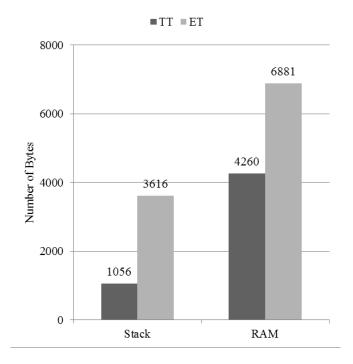

| Figure 9-11 Memory and stack utilization of ET and TT design for DAQ system                                                                                      |

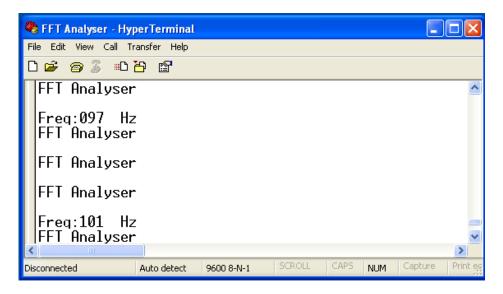

| Figure 9-12 A sample output shown using hyper terminal from the FFT/ADC framework171                                                                             |

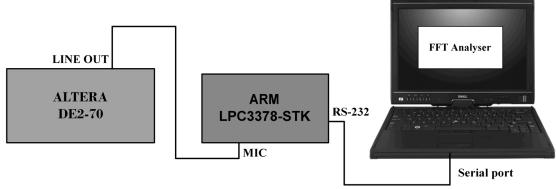

| Figure 9-13 The 'FFT Analyser' frame work                                                                                                                        |

| Figure 9-14 One possible order of patterns to be followed which can lead to a TT design for the FFT Analyser                                                     |

| Figure 9-15 Comparison of CPU utilization, idle time and power consumption by ET and TT designs for the FFT Analyser                                             |

| Figure 9-16 Comparison of memory utilization by the ET and TTH designs of the FFT Analyser                                                                       |

| Figure 10-1 Pattern life cycle [Adapted from (Petter et al, 2010)]190                                                                                            |

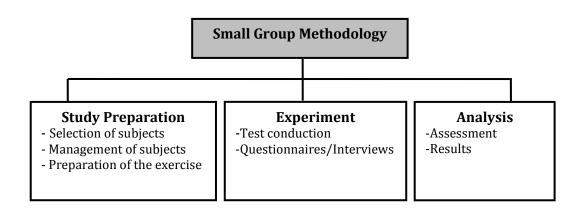

| Figure 10-2 An overview of the SGM technique195                                                                                                                  |

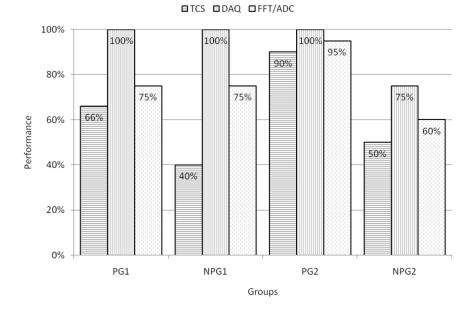

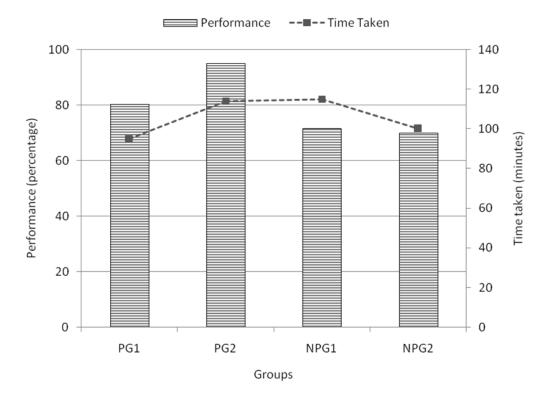

| Figure 10-3 Performance of groups (Experiment 1)204                                                                                                              |

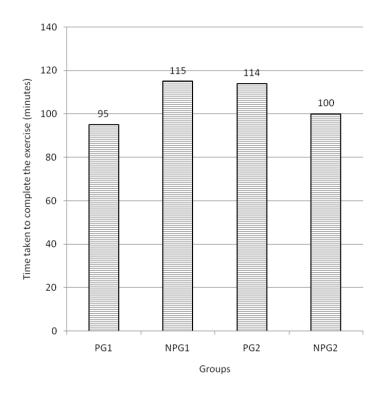

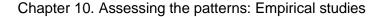

| Figure 10-4 Time taken by each group to complete the exercise (Experiment 1)207                                                                                  |

| Figure 10-5 Structural layout used for documenting patterns in the PMES collection209                                                                            |

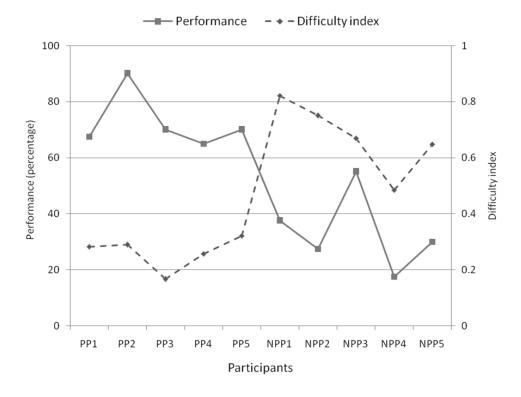

| Figure 10-6 Performance of participants (Experiment 2)214                                                                                                        |

| Figure 10-7 Time taken by the participants to complete the exercise (Experiment 2)216                                                                            |

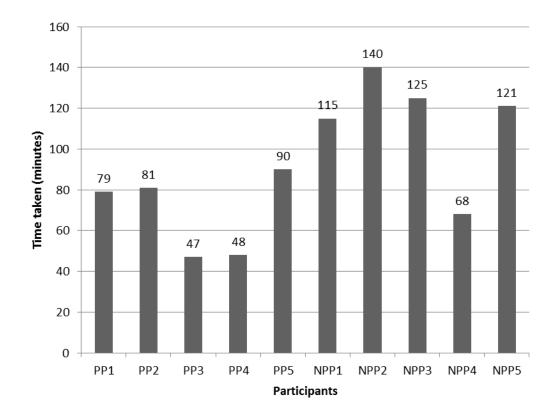

| Figure 10-8 Feedback from the participants regarding the difficulty level of the exercise218                                                                     |

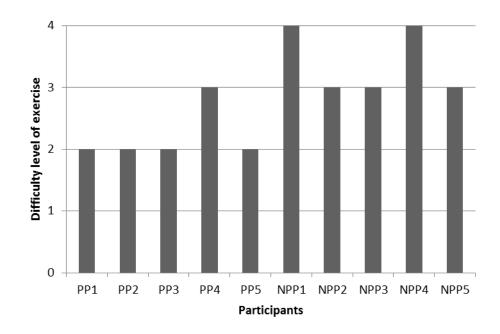

| Figure 10-9 Feedback of the participants about the value of the material provided219                                                                             |

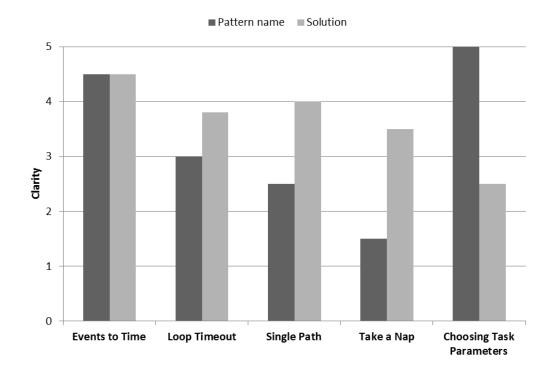

| Figure 10-10 Feedback about pattern names and solution (1-5) 1 = Lowest, 5 = Highest 221                                                                         |

| Figure 10-11 Summary of results (Experiment 1)223                                                                                                                |

| Figure 10-12 Summary of results (Experiment 2)225                                                                                                                |

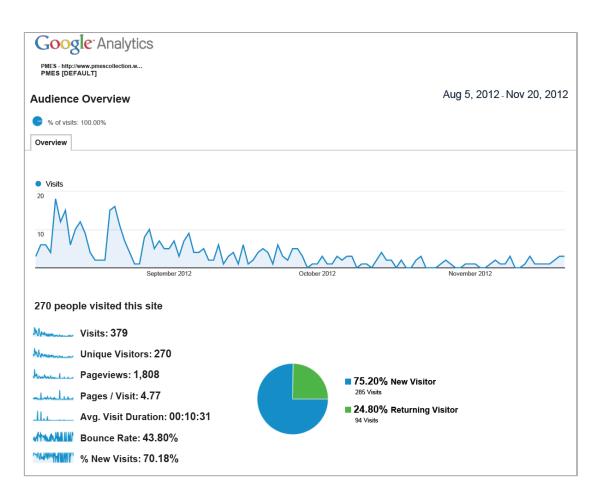

| Figure 11-1 A preview of the Google analytics report: An account created to monitor the statistics on the visitors for the website www.pmescollection.weebly.com |

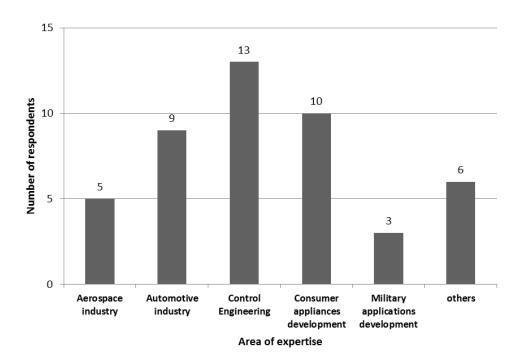

| Figure 11-2 Respondents area of expertise                                                                                                                        |

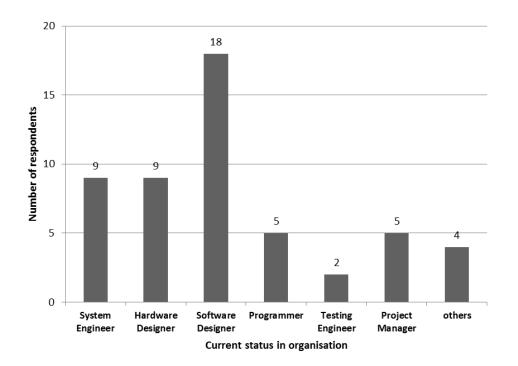

| Figure 11-3 Respondents current status in organisation242                                                                                                        |

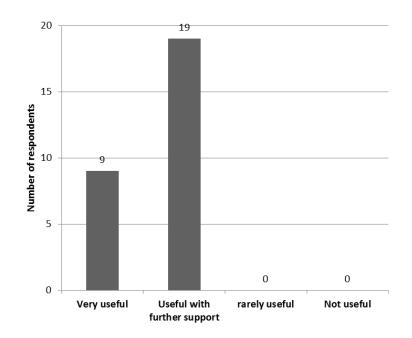

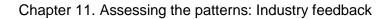

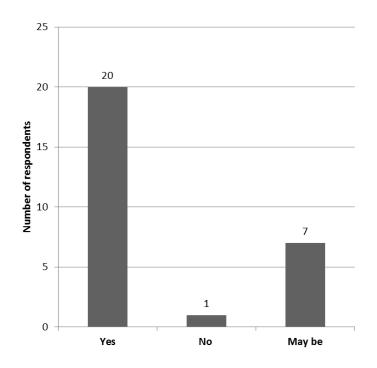

Figure 11-11 Illustrating the number of coding references cover for each node......258

# LIST OF TABLES

| Table 3-1 Summary of comparison between a design patterns repository and an expert system         |

|---------------------------------------------------------------------------------------------------|

| Table 4-1 Task specifications for a system with non-pre-emptive cyclic executive scheduler.43     |

| Table 4-2 Task specifications for task set required to be scheduled with a co-operative scheduler |

| Table 4-3 Task set specifications required to be scheduled with a hybrid scheduler56              |

| Table 4-4 Comparative view of event-triggered and time-triggered architectures         59         |

| Table 6-1 Pattern forms95                                                                         |

| Table 7-1 Comparison between the 'PTTES' collection and the 'PMES' collection                     |

| Table 7-2 Jitter measurements for the Un-Balanced System                                          |

| Table 7-3 Jitter measurements for the Balanced System       118                                   |

| Table 8-1 Thumbnails of patterns in the PMES language       126                                   |

| Table 9-1 Specifications of the periodic tasks in ET design for DAQ system                        |

| Table 9-2 Performance measures for the ET design for DAQ system       158                         |

| Table 9-3 Task specifications of TTC design for DAQ system                                        |

| Table 9-4 Comparison of ET and TT design for DAQ system       166                                 |

| Table 9-5 Task specifications of the periodic task in the ET design for FFT Analyser173           |

| Table 9-6 Task specifications of TT design for FFT Analyser       175                             |

| Table 9-7 Performance measures of ET and TT design for FFT Analyser         176                   |

| Table 9-8 Jitter comparison for TTH and TTH-PP designs178                                         |

| Table 10-1 Criteria for evaluating patterns [Adapted from (Petter et al, 2010)]191                |

| Table 10-2 Difficulty levels of systems used in exercise for experiment 1                         |

| Table 10-3 Group structure for Experiment 1    202                                                |

| Table 10-4 Performance of groups (Experiment 1)    204                                            |

| Table 10-5 Overall average performance of groups in the exercise         205                      |

| Table 10-6 Calculations for the difference in mean of PG and NPG groups206                        |

| Table 10-7 Participants in the study                                                              |

| Table 10-8 Details of the tasks given in the exercise (Experiment 2)  | 211 |

|-----------------------------------------------------------------------|-----|

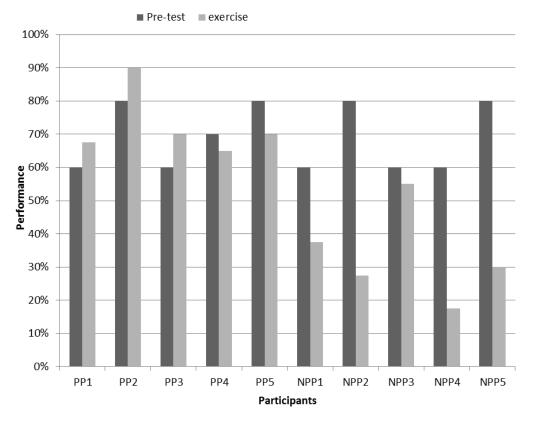

| Table 10-9 Performance of students in Experiment 2                    | 214 |

| Table 10-10 Overall average performance of PP and NPP (Experiment 2)  | 215 |

| Table 10-11 Calculations for the differences of mean for experiment 2 | 217 |

| Table 11-1 Distribution of comments under various nodes               | 257 |

A number of papers were published during the course of the work described in this thesis. These are listed below in reverse chronological order.

#### **Directly-related publications**

- Lakhani, F. and Pont, M. J. (2012) "Empirical studies for the assessment of the effectiveness of design patterns in migration between software architectures of embedded applications". Journal of Software Engineering International Scholarly Research Network (ISRN), Volume 2012 Article ID: 259064 ISSN: 2090-7680 doi:10.5402/2012/259064

- Lakhani, F. and Pont, M. J. (2012) "Applying design patterns to improve the reliability of embedded applications through a process of architecture migration". Proceedings of the 9<sup>th</sup> IEEE International Conference on Embedded Systems and Software (ICESS 2012), Liverpool, UK. IEEE Computer Society: pp1563-1570

- 3. Lakhani, F., Wang, H. and Pont, M. J. (2011) "Supporting the migration between event-triggered and time-triggered software architectures: A small pattern collection intended for use by the developers of reliable embedded systems". Technical report ESRG 2011-09-01.

- Lakhani, F., Pont, M.J. and Das, A. (2010) "Improving the reliability of embedded systems as complexity increases: supporting the migration between event-triggered and time-triggered software architectures" Proceedings of the 15<sup>th</sup> Annual European Conference on Pattern Languages of Programming EuroPLoP'10, Irsee, Germany. Published by ACM New York, NY, USA. ISBN: 978-1-4503-0259-3

- Lakhani, F. and Pont, M.J. (2010) "Using design patterns to support the migration between different system architectures" Proceedings of the 5<sup>th</sup> IEEE International Conference on Systems of Systems Engineering (SoSE), June 2010, Loughborough, UK: pp1-6.

- Lakhani, F. and Pont, M.J. (2010) "Code balancing as a philosophy for change: Helping developers to migrate from event-triggered to timetriggered architectures" Proceedings of the 2010 UK Electronics Forum, 30 June - 1 July 2010, Newcastle, UK, Published by Newcastle University. ISBN: 978-0-7017-0232-8

- Lakhani, F., Pont, M.J. and Das, A. (2009) "Towards a pattern language which supports the migration of systems from an event-triggered preemptive to a time-triggered co-operative software architecture" Proceedings of the 14<sup>th</sup> Annual European Conference on Pattern Languages of Programming EuroPLoP'09, Irsee, Germany, 8-12 July

2009. Published by CEUR, volume 566, ISSN: 1613-0073: pp. F2-2 to F2-25

Lakhani, F., Pont, M.J. and Das, A. (2009) "Can we support the migration from event-triggered to time-triggered architectures using design patterns?" Proceedings of the 5<sup>th</sup> UK Embedded Forum, Leicester, UK, pp. 62-67. Published by Newcastle University. ISBN: 978-0-7017-0222-9.

#### **Associated publications**

Das, A., Lakhani, F., Gendy, A.K and Pont, M.J (2009). "Two simple patterns to support the development of reliable real-time embedded systems" 14th European Conference on Pattern Languages of Programs, EuroPLoP'09 (Kloster Irsee, Germany, 8 – 12 July 2009)

#### **Poster publications**

- 10. Lakhani, F. and Pont, M.J. "Best practices for engineers to design safer systems", poster selected for presentation at the University of Leicester, Festival of Post Graduate Research (Leicester, UK, June 2011).

- 11. Lakhani, F. and Pont, M.J. "Building in' safety in the electronic age", poster selected for presentation at the University of Leicester, Festival of Post Graduate Research (Leicester, UK, June 2010).

- 12. Lakhani, F. and Pont, M.J. "Staying safe in a world full of silicon chips", poster selected for presentation at the University of Leicester, Festival of Post graduate Research (Leicester, UK, June 2009).

# LIST OF ABBREVIATIONS, SYMBOLS AND UNITS

| Abbreviations |                                                                    |

|---------------|--------------------------------------------------------------------|

| ADC           | Analogue-to-Digital Converter                                      |

| BCET          | Best-Case Execution Time                                           |

| CAGR          | Compound Annual Growth Rate                                        |

| CAN           | Controller Area Network                                            |

| CCS           | Cruise-Control System                                              |

| CDRH          | Center for Devices and Radiological Health                         |

| CPU           | Central Processing Unit                                            |

| DAQ           | Data Acquisition                                                   |

| DM            | Deadline Monotonic                                                 |

| EDF           | Earliest Deadline First                                            |

| ET            | Event-Triggered                                                    |

| FFT           | Fast Fourier Transform                                             |

| GCD           | Greatest Common Divisor                                            |

| GoF           | Gang of Four                                                       |

| GPIO          | General Purpose Input Output                                       |

| LCM           | Least Common Multiple                                              |

| LLF           | Least Laxity First                                                 |

| MC            | Mission Computer                                                   |

| NOP           | No Operation                                                       |

| NPG           | Non- Pattern Group                                                 |

| NPP           | Non-Pattern Participant                                            |

| OED           | Oxford English Dictionary                                          |

| OFP           | Operational Flight Program                                         |

| PG            | Pattern Group                                                      |

| PIE           | Pattern Implementation Example                                     |

| PLoP          | Pattern Languages of Programming                                   |

| PMES          | Patterns for Migrating Embedded Systems                            |

| PP            | Pattern Participant                                                |

| PTTES         | Patterns for Time-Triggered Embedded Systems                       |

| QWAN          | Quality Without A Name                                             |

| RM            | Rate Monotonic                                                     |

| RTSC          | Real-Time System Compiler                                          |

| SPE<br>TT     | Synergistic Processor Element                                      |

| TTC           | Time-Triggered                                                     |

| TTCAN         | Time-Triggered Co-operative Time-Triggered Controller Area Network |

| TTH           | Time-Triggered Hybrid                                              |

| TTP           | Time-Triggered Pre-emptive                                         |

| UML           | Unified Modelling Language                                         |

| WCET          | Worst-Case Execution Time                                          |

|               |                                                                    |

## Symbols

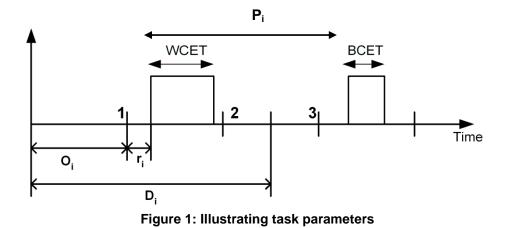

| ARJ <sub>i</sub>      | Absolute release jitter observed for task <i>i</i> |

|-----------------------|----------------------------------------------------|

| Ci                    | Execution time of Task i                           |

| CPU <sub>active</sub> | Processor busy time                                |

| CPU <sub>idle</sub>   | Processor idle time                                |

| Di                          | Relative Deadline of task <i>i</i>                |

|-----------------------------|---------------------------------------------------|

| I <sub>CPU</sub>            | Average current consumption by the processor      |

| I <sub>DD(DCDC)active</sub> | Active mode DC-to-DC converter supply current     |

| IDD(DCDC)pd                 | Power-down mode DC-to-DC converter supply current |

| n                           | Number of tasks                                   |

| P <sub>CPU</sub>            | Average power consumption by the processor        |

| p <sub>i</sub>              | Period of task i                                  |

| r <sub>i</sub>              | Release time of task <i>i</i>                     |

| Si                          | Start time of task <i>i</i>                       |

| U                           | Processor utilisation                             |

| V <sub>CPU</sub>            | Average voltage across the processor              |

## Units

| ms    | Milliseconds |                  |         |

|-------|--------------|------------------|---------|

| µsecs | Microseconds | 10 <sup>-6</sup> | seconds |

## **PART A: INTRODUCTION**

This thesis is divided into several parts and this first part provides an introduction to the work presented as follows:

- 1. The overview of the embedded systems field and the description of the research problem and contributions are described in CHAPTER 1.

- 2. CHAPTER 2 describes the motivating examples from the literature which have provided the driving force to establish the research problem.

- 3. CHAPTER 3 discusses the methodology adopted for the research.

Chapter 1. Introduction

## **CHAPTER 1. INTRODUCTION**

#### **1.1. Introduction to the problem**

This thesis is concerned with the development and evaluation of novel techniques that will help to improve the reliability of what are known as "embedded systems".

In the 1930-40s, computers were very large and expensive. Given this, it is not surprising that Thomas Watson (1943) said: *"I think there is a world market for may be five computers."* The world market has changed beyond recognition since that time. The huge computers of Watson's time have now been replaced by literally millions of much smaller "desktop", "laptop" and "handheld" computers powered by *embedded* processors.

While desktop computers perform multiple functions, an embedded system is a special-purpose computer system which is designed to perform a small number of dedicated functions for a specific application. More formally, "An embedded system is an application that contains at least one programmable computer (typically in the form of a microcontroller, a microprocessor or digital signal processor chip) and which is used by individuals who are, in the main, unaware that the system is computer based" (Pont, 2001).

Despite the ubiquitous nature of desktop and laptop computers, they represent only the tip of the iceberg when it comes to estimating computer numbers. For every processor used in a familiar desktop or laptop computer, around 100 processors are "embedded" in computer systems as widespread as aircraft,

#### Chapter 1. Introduction

automotive vehicles, medical equipment, children's toys and DVD players (Barr, 1999; Li and Yao, 2003). They are also part of many of the electrical appliances used at home, for example, air-conditioners, irons, kettles, microwaves, refrigerators and washing machines etc. Outside homes, these processors work in automatic doors, CCTVs, escalators, intruder alarms, lifts, traffic light signals, vending machines and many other devices. In most cases, these embedded processors are a key part of the systems they inhabit, for example, around a third of the cost of developing many new cars is spent on the vehicle electronic and software systems (Bouyssounouse and Sifakis, 2005). The luxury 7-Series BMW and S-class Mercedes boast about 100 processors apiece (Turley, 2003) and these processors are in many cases serving to provide either comfort or safety, for example window and engine control and anti-braking systems in the cars.

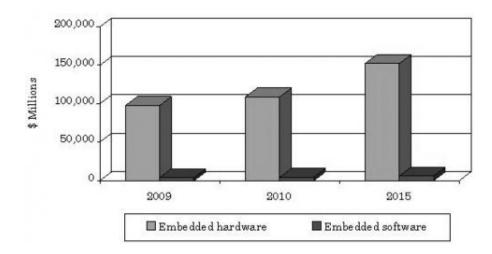

Being in such widespread use, embedded processors have a huge international market. According to a recent study by BCC research (Business Communications Company – a publisher of technology market research reports), the global market for embedded systems is expected to increase from US\$101.6 billion in 2009 to an estimated US\$158.6 billion by the end of 2015, a compound annual growth rate (CAGR) of 7%. Embedded hardware was worth US\$108.8 billion in 2010 and is expected to grow at a CAGR of 7% to reach US\$152.4 billion in 2015. Embedded software generated US\$4.2 billion in 2010 and is expected to increase to US\$6.1 billion in 2015 (BCC, 2012). The growth statistics are shown in Figure 1-1.

3

Figure 1-1 Embedded systems market 2009-2015 (Source: BCC research)

The huge growth in demand for these systems and the great increase in their complexity mean that reliability is a critical issue in the design of such systems. This is important not just to meet the needs of businesses involved in manufacturing reliable products, but also because people in developed countries are reliant on many embedded designs in systems such as aircraft, cars and medical equipment for their safety.

Although embedded applications are an essential (though mostly hidden) part of everyday life, the process of developing safe and reliable applications remains a highly challenging and complex aspect of the design and test process. Developers and designers of embedded applications face huge technical challenges such as meeting all the timing constraints, limited memory space, and restrictions on power usage. Graaf *et al* (2003) have argued that despite all the advancements such as application development tools and techniques, existing software development techniques have failed to address the challenges faced by the developers of embedded applications. This argument is supported by the fact that firms producing such devices still find it difficult to produce completely defect-free devices. For example, the Centre for Devices and Radiological Health (CDRH) reported that in 2006, 21% of all medical device recalls were for software defects (Krasner, 2010).

#### **1.2.** Description of the problem addressed in this thesis

The main focus of the research presented in this thesis revolves around two key software architectures used in developing modern embedded applications: these are termed as "event-triggered" and "time-triggered".

For many developers, event-triggered (or "ET") architectures are more familiar. ET designs involve creating systems which handle multiple interrupts. For example, interrupts may arise from periodic timer overflows, the arrival of messages on a serial communication bus, the pressing of a switch, the completion of an analogue-to-digital conversion (ADC) and so on. To create ET systems, the developer may write code to handle the various events either directly: this will typically involve creating an "Interrupt Service Routine" (ISR) to deal with each event. Alternatively, the event will be handled slightly less directly through use of a real-time operating system.

The alternative to an event-triggered architecture is a time-triggered ("TT") architecture. When implementing TT systems, there is only one interrupt enabled. This single interrupt is usually linked to a timer "Tick", which might occur (for example) every millisecond: this tick, in turn, drives all software activity in the system.

5

Both ET and TT architectures have their own strengths and weaknesses. The main strength of TT architecture is its ability to enable systems to be more 'predictable' (Nissanke, 1997; Pont, 2001; Kopetz and Bauer, 2002; Albert and Bosch GmbH, 2004). Since highly predictable system behaviour is an important design requirement for many embedded systems, TT software architectures have become the subject of considerable attention. It has been widely accepted that the TT architecture is a suitable candidate for many safety-critical applications since they help to improve overall safety and reliability (Allworth, 1981; Nissanke, 1997; Bate, 1998). For example, TT architectures have been accepted as a generic solution for highly dependable<sup>1</sup> systems such as X-by-Wire<sup>2</sup> systems (Ayavoo, Pont et al., 2005; Ayavoo, 2006). However, even in more mundane domestic applications (e.g. an alarm clock that fails to sound on time or a video recorder that operates intermittently) where failure is relatively inconsequential, poor reliability can have other impacts such as reduced sales etc. Besides being predictable in nature, TT systems are also easy to validate, test and certify (Liu, 2000).

The published literature provides many examples of embedded applications such as those discussed in (Shepard and Gagne, 1990; Kubinger and Humenberger, 2004; Turley, 2009) for which the ET architecture is initially preferred because of the perceived benefits they offer such as flexibility in design and their ability to respond more quickly upon arrival of any internal or

<sup>&</sup>lt;sup>1</sup> Dependability is a measure of whether a system can be relied upon to perform the desired action. Kopetz (1997) and Hanmer (2007) define the different attributes of dependability such as reliability, safety, availability and security.

<sup>&</sup>lt;sup>2</sup> X-by-Wire systems are electronic systems without mechanical backup where the 'X' stands for the safety related applications such as steering and braking. Some keywords in automotive systems are "accelerate-by-wire", "steer-by-wire" and "brake-by-wire".

external events. Later in their life cycle these applications exhibit problems related to reliability and therefore migrated to TT architecture.

It is therefore realised that to accomplish reliable software systems especially where safety is a critical issue migration between software architectures becomes crucial to achieve systems that are more predictable and safer. However, it is also accepted by the expert's community that migrating software architectures in embedded applications offers various challenges. It may be tempting to assume that conversion between ET and TT designs will simply involve converting all event-handling software routines into periodic activities. However, the required software changes are – in many cases – much more profound. For example changes to one part of the software may affect other inter-linked parts and so a thorough analysis of the migrating system is necessary before making any substantial changes. The overall goal of the work presented in this thesis is to identify ways in which the work involved in migrating between existing ET architectures and "equivalent" and effective TT architectures could be reduced.

As the research is motivated by providing support during the process of architecture migration, for this purpose research has explored the concept of 'Design Patterns'. Design patterns emerged from the field of architecture and gained popularity in diverse disciplines. Design patterns are well-documented, time-tested solutions to classic design problems and capture significant domain knowledge. In the field of embedded systems most of the previous research work (Adams, Coplien *et al.*, 1996; Bottomley, 1999; Pont, 2001;

7

Herzner, Kubinger *et al.*, 2005; Cloutier and Verma, 2007; Eloranta, Koski *et al.*, 2009) focused on documenting patterns for system construction. However, design patterns which could assist embedded system practitioners in the process of migration of architecture has been somewhat neglected. The research presented in this thesis aims to explore how this gap might be bridged.

#### 1.2.1. Research premise and goal

The work presented in this thesis began with the premise that – for many embedded systems which are implemented using an ET architecture – migration to a TT architecture would improve reliability.

From this starting point, it was accepted that altering the system architecture would not be a trivial process and the core research goal was to explore whether an appropriate set of 'design patterns' could be used to facilitate this transition.

### **1.3. Research contributions**

The research described in this thesis makes the following contributions:

- It has explored the need for migration from existing event-triggered architectures to time-triggered architectures in order to improve system reliability.

- It has explored the challenges involved in the migration process from event-triggered to time-triggered architectures.

8

- This research has explored for the first time ways in which design patterns can be used to support the migration between event-triggered and time-triggered software architectures and resulted in the development of a pattern language to support the migration process.

The pattern language is introduced by identifying links between previously proposed patterns by peers and the new patterns proposed during the course of this research.

- The research has also performed the rigorous assessment of the pattern language as follows:

- By demonstrating the applicability of the proposed patterns on real applications through laboratory experiments.

- By conducting controlled experiments with a target audience of users.

- Through an industrial survey to obtain feedback from the practitioners on how the proposed patterns could be useful in the industrial context.

### **1.4. Outline of the thesis**

This thesis is structured as follows.

- Part A Introduction:

- CHAPTER 1 provides the relevant background information to the research problem undertaken and describes the contributions made by this research.

- CHAPTER 2 explains the motivating example systems from the literature which helped in the formulation of the research problem.

- CHAPTER 3 describes the research methodology adopted in detail.

- Part B Literature Review:

- CHAPTER 4 provides a discussion on the two main software architectures (event-triggered and time-triggered) which is the focus of this research. Related to this the chapter also explains different scheduling schemes which constitute the software architectures. The chapter also provides a comparison of the two architectures as discussed in the published literature.

- CHAPTER 5 describes the problem of migration that embedded applications face during their life cycle. This chapter presents details on reasons for migration in embedded systems and dependencies between components and the related work carried out by previous researchers in the field.

- CHAPTER 6 introduces the concept of design patterns and their historical background. It briefly discusses how this concept was acknowledged by experts in diverse fields and their acceptance and implementation. The chapter also discusses the process of applying design patterns in building embedded applications, and how and why they can assist the developers of embedded applications.

- Part C Development and evaluation of patterns for migration:

- CHAPTER 7 describes the derivation process for the patterns.

- CHAPTER 8 introduces a new collection of design patterns proposed with the aim of helping developers in migrating from event-triggered architectures to time-triggered architectures. It also discusses new patterns that are introduced by this research.

- CHAPTER 9 demonstrates the use of the proposed pattern collection with case studies and examples of how various patterns can be applied during the migration process from eventtriggered design to a time-triggered design.

- CHAPTER 10 presents the evaluation process of the newly proposed patterns and the empirical studies used in the process.

- CHAPTER 11 presents the evaluation of the patterns in the industrial context. This is achieved using the web-based survey with employees in the software industry and a website was also developed for this purpose.

- CHAPTER 12 is dedicated to conclusions and the future expansion of this research that could further enhance the initial steps taken.

- Part D Appendices: The appendices include supplementary materials related to this thesis.

- Appendix A describes different pattern forms found in the literature.

- Appendix B contains full specifications of the patterns that are derived and documented during the research.

- Appendix C contains the exercises designed for use during the empirical evaluation of the research.

- Appendix D contains the documents related to industrial evaluation of the research.

- Appendix E provides the bibliographic references to all the citations used.

### 1.5. Conclusions

This introductory chapter has provided a summary of the overall theme of the work described in this thesis. The discussion regarding software architectures indicated that several embedded applications may demand change in their existing architecture during the course of their life cycle due to issues with reliability and safety. This change in architecture offers various challenges to the designers/developers of embedded applications which have often been overlooked by previous research work in the field resulting in a lack of support for the designers to tackle the situation. In order to solve this and overcome some of the difficulties involved in the migration process this research presents the novel idea of using design patterns. Based on these discussions the main goal and key contributions made by this research were stated and the layout of the thesis provided.

The remainder of this thesis will describe the work undertaken by this research.

## **CHAPTER 2. MOTIVATING EXAMPLES**

### 2.1. Introduction

As outlined in CHAPTER 1, the main objective of the work presented in this thesis was to develop and assess techniques that will improve the reliability of existing software applications through a process of architecture migration.

In order to explain the motivation for this work, this chapter summarises some representative examples that have been found in the literature (Section 2.2 to Section 2.4). Section 2.5 provides a discussion based on the examples described and the relevant concerns of the research and conclusions are given in Section 2.6.

### 2.2. The F-18 Mission Computer

The case study related to a F/A-18 aircraft has provided the motivation to explore the need for migration between different software architectures for complex embedded applications. The F/A-18 aircraft is also referred to as CF-188 by the Canadian Forces and was manufactured by McDonnell Douglas Corporation. The case study is presented in detail in (Shepard and Gagne, 1990).

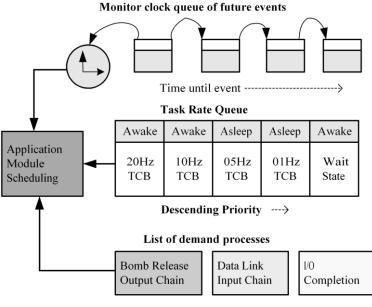

Maintenance problems were reported for F/A-18 Mission Computer (MC) Operational Flight Program (OFP) when some modifications were required in the system. A block diagram representing the runtime scheduler for this system is shown in Figure 2-1.

Descending Priority ---→

Figure 2-1 Model of F-18 MC [adapted from (Shepard and Gagne, 1990)]

The system model was based on a pre-emptive scheduling process (such a process is described in more detail in Section 4.2.2: the details are not relevant here). The model was based on a design that was required to run periodic processes (grouped into four separate task rates of 20, 10, 5 and 1 Hz) as well as interrupt service routines (termed as demand routines by authors) for bomb release, data link input, I/O completion, and I/O fault recovery.

The relative priorities of the task rates is reflected in the structure of the 'Task Rate Queue', implemented as a linked list. This queue contains one Task Control Block (TCB) for each task rate. The TCB indicates the status of the task rate (awake or asleep) and provides storage for control information

#### Chapter 2. Motivating Examples

related to that rate. The occurrence of interrupts pre-empts the currently running tasks. Once the interrupt processing is finished, the pre-empted task processing is resumed.

#### 2.2.1. Problems with the existing model of the F-18 MC

The major problem reported with the system was failure to observe all the timing constraints when new software components were added. With the existing model it was also difficult to guarantee that any alterations in the system did not alter the logical correctness of the system. Further, the testing methodology was not comprehensive enough to satisfy all constraints. All these factors highlighted the need for a scheduling methodology which would enable verification of the timing constraints of the system before its operation and easy testing of the system. In other words, predictable behaviour was the main requirement of the modified system.

#### 2.2.2. Migration to pre-runtime scheduling

Because of the problems with the existing model, it was decided to shift the entire system to pre-runtime scheduling to make it possible to verify all the timing constraints in advance. However, it was a big challenge to convert such a complex system to pre-runtime scheduling. This involved an extensive review of the complete OFP source code, a study of 2500 pages of technical documentation and a review of 2400 software routines. Flow charts were generated to understand the scheduling requirements of the OFP and all the interrupt service routines were converted to periodic processes (this is described as a 'polling solution'). This resulted in a 95% reduction of the interrupts being generated by the system. The schedules were generated to

run all the tasks in the system along with their release times, execution times and deadlines.

#### 2.2.3. Performance improvement after migration

Shepard and Gagne (1990) have reported the following improvements in the transformed pre-runtime model of the F-18 MC:

- As the major problem with the system is testing and verification after adding new modules, migration to pre-runtime scheduling has made the testing process far easier and less labour intensive.

- To guarantee reliable system behaviour in the case of complex embedded applications it is important to predict maximum CPU load and I/O processing capacities during the design stage. Transformation of the system from pre-emptive scheduling to pre-runtime scheduling helped in achieving this.

- As pre-runtime scheduling enable offline schedules to be made this helped in facilitating the timing requirements for all the system processes in advance.

- Pre-runtime scheduling also significantly reduced the number of context switches in the system. With the previous model based on pre-emptive scheduling approximately 1000 context switches were estimated per second incurring significant overhead. Pre-runtime scheduling was helpful in countering this problem.

## 2.3. Migration towards time-triggered image acquisition

The second example found in the literature that justified this research is a case study based on replacing a time-triggered model for the existing event-

#### Chapter 2. Motivating Examples

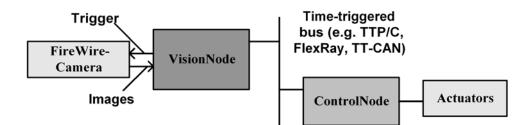

triggered model for an image processing application (Kubinger and Humenberger, 2004). For this application there was a preference for TT architecture as the existing design based on ET architecture was observed to have variations in the sampling time which increased the probability of data (images) loss. Also the TT architecture can have fixed latency, low jitter values and predictable behaviour. The researchers aimed to investigate the interfacing issues between cameras and TT architectures and to achieve a jitter-free and synchronized sequence of images. The objective was to achieve a guaranteed behaviour of the camera such that the system must finish processing of image 'n' when image 'n+1' arrives. Their proposed TT model (distributed in nature) makes use of a TT bus (for example TTP/C, FlexRay or TTCAN). The bus used the TDMA (Time Division Multiple Access) principle and each message is assigned a periodic time slot which made it possible to precisely control the triggering of the camera and acquisition and transfer of the images from the camera to the node. The layout of the concept is shown in Figure 2-2.

Figure 2-2 Layout of the vision-based distributed embedded control application [Adapted from (Kubinger and Humenberger, 2004)]

They have demonstrated the application of their proposed approach using a SONY FireWire-camera DFW-VL500 on a 400 Mbps FireWire bus. They also presented the comparative results of ET and TT models. The results showed

less latency values (highly varying) for the ET model and jitter<sup>3</sup> values of 33.33ms. On the other hand, the TT model showed high but fixed values of latency and jitter values in the microseconds range only.

#### 2.4. Sony® cell processor

This example is quoted by Jim Turley in (Turley, 2009). He reported an interesting case observed by the programmers of Sony Corporation published in 'Embedded use of the Cell processor' (Kawamura, Yamazaki *et al.*, 2008). Half of the cell chip is dedicated to eight identical Synergistic Processor Elements (SPEs) having their own instruction set unique to the cell. Each SPE is a 128-bit single-instruction, multiple-data (SIMD) vector processing machine and has its own 256K block of private RAM for executing code or storing local data. The Linux distribution for the cell treats the SPEs as virtualized resources; this resulted in the creation of more SPE threads than there are SPEs. The overhead of this feature is that one SPE might be swapped out while it is running. To avoid this, the Sony team "pinned" the network stack to one SPE, effectively prohibiting Linux from swapping it out and dedicating that SPE exclusively to network processing.

The problem observed with the system can best be illustrated by citing a passage from (Turley, 2009). *"Given the high packet rates Sony was hoping for, frequent interrupts turned from being a necessity to being a problem. In their experience, most network stacks are interrupt-driven, especially from the*

<sup>&</sup>lt;sup>3</sup> Jitter refers to the deviation from the ideal timing of an event and can have a serious impact on system reliability. More details are explained in Chapter 6

#### Chapter 2. Motivating Examples

hardware interface when it needs servicing. As data rates climb, these interrupts (and their attendant context switching) become so frequent that the overhead overwhelms the actual task. The faster it works, the slower it goes." The solution reported in the article was based on the removal of interrupts from the system. "To fix this, the team decided to switch from an interruptdriven to software polled design. They kept the same hardware components but just tweaked the network driver to poll the chip at regular timer tickintervals. The resulting efficiency was dramatic."

This example shows that an interrupt-driven architecture initially chosen to make the system more responsive can ultimately jeopardise the whole system in situations of high load. Finally a software based polling mechanism was adopted to overcome the problem and was found to be very effective.

#### 2.5. Discussion

In this chapter three examples from the literature are described that highlight the need for migration of existing event-triggered and/or interrupt-driven software architectures in embedded applications to time-triggered architectures in order to improve system reliability.

The F-18 aircraft example discussed in Section 2.2 is an example of high reliability high integrity embedded application for which all the necessary issues were considered at the design time and so a priority based pre-emptive task model was chosen. The selected architecture did not proved a wise

19

#### Chapter 2. Motivating Examples

choice in the later stages when the application required new software components to be added. The testing of the application was another issue that arose when alterations were made to the existing model. The aircraft was then migrated to pre-runtime scheduling model which facilitated the testing and verification process and showed improvement in system reliability along with the reduced system overheads such as CPU and memory utilization. The transformation process itself however was labour intensive involving heavy technical documentation reviews in order to make necessary changes in the code.

The second example discussed in Section 2.3 for the image processing application also showed considerable improvement in jitter values (from the millisecond range to the microsecond range) when transformed to timetriggered architecture from its existing event-triggered design. The rationale for the transformation was described as possible loss of data with the existing model. The transformation process involved the use of a time-based communication protocol and periodic scheduling of task at the design time which itself involved a number of design decisions for optimised system performance which are not considered in the study described by the authors.

The third example is a commercial product developed by the Sony Corporation in which the migration from interrupt-driven architecture to polledinput design helped to overcome the problems when the application was subjected to peak load situations. However it is assumed that for commercially

### Chapter 2. Motivating Examples

confidential reasons the example does not discuss how the challenge was faced and what the major concerns were during the transformation process.

The examples discussed have provided the motivation to:

- Further explore the need of migration from event-triggered architectures to time-triggered architectures in order to improve system reliability.

- Explore the possibilities of some kind of support which could assist the developers in making better choices among a variety of possible timetriggered architectures. This would enable developers to take better informed decisions during the migration process from event-triggered design to time-triggered designs.

# 2.6. Conclusion

This chapter has presented three examples from the literature to highlight the requirements for changes in software architecture of an application later in its life cycle. All of the three applications were designed with an architecture where multiple interrupts are made active to handle any input data. The examples have demonstrated that in such architectures the need to change may arise for problems due to system performance and reliability in peak load situations, when new components are added and where further testing or verification processes are needed. In all the three examples the architecture was transformed to remove multiple interrupts and so a time-based architecture was chosen in which offline schedule plans can be enabled to predict system behaviour in advance. These examples helped in building the

### Chapter 2. Motivating Examples

overall argument for the research problem that proposed that migrating applications to an architecture where single interrupt can handle all system activities may help in improving system reliability.

The next chapter explains the overall research process and the choice of methodology adopted to meet the challenges of this research.

# CHAPTER 3. METHODOLOGY

# 3.1. Introduction

A methodology in research refers to the theoretical argument and investigative framework that researchers use in order to justify their research methods and the design of their experimental investigations (Case and Light, 2011). This chapter describes the methodology adopted to conduct the research presented in this thesis.

This chapter organized as follows. Section 3.2 presents a general overview of the methodology adopted by the research, Section 3.3 discusses the rationale behind the formulation of the research problem, and Section 3.4 describes the steps involved in building the hypothesis and setting goals for the research in order to test the hypothesis. Following this, Section 3.5 explains the research work that involves derivation of design patterns and experimental work to test and implement the patterns. Section 3.6 explains the methodology adopted to evaluate the research and the chapter conclusions are presented in Section 3.7.

# 3.2. General approach to the investigation

In common with most research projects, the work presented in this thesis has evolved in stages and each stage has been subject to several iterations. In a wider sense the process of identifying a valid research problem, identifying a proposed solution to a problem, developing the solution, and then testing and verifying the solution, is identical to the process generally described as 'The

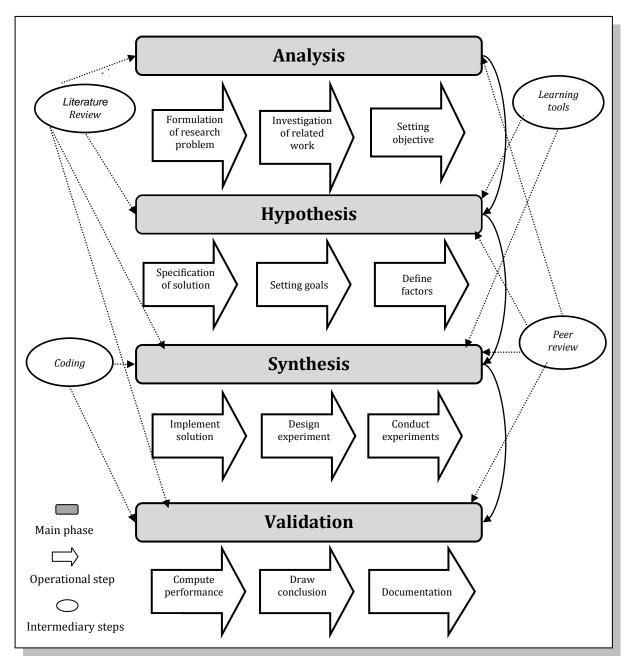

Scientific Method' first formulated over 400 years ago (Gower, 1997). The Scientific Method of course also tacitly underpinned and guided the technical work described in the thesis. The definition of the modern scientific method as described in (Bock, 2001) is: *"The Scientific method comprises four sequential phases – Analysis, Hypothesis, Synthesis and Validation – which are applied to a task iteratively and recursively to achieve the objective of the task."* A research process is in fact similar to undertaking a journey in which a person must decide where he/she wants to go and which route to take. The problem is compounded in deciding which one is the best to follow if there is more than one possibility to get to the destination. Similarly a research process is all about deciding what to do, planning how to do it and then doing what is considered as appropriate in the existing scenario.

The next few sections will describe how this research underwent several stages from the initial point of formulation of the research problem, to setting goals, choosing the appropriate methodology at each step during the research, and evaluating the final outcome.

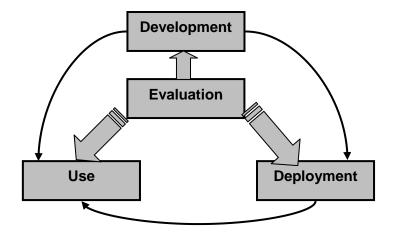

The process is described as phases of analysis, hypothesis, synthesis and validation and each phase was broken down into further operational steps as depicted in Figure 3-1.

Figure 3-1 Illustrating the different steps taken during the main phases of the research process

# 3.3. Formulation of the research problem

The research was initiated with the literature review in order to gain a thorough understanding of the domain of embedded systems design. In this initial process both the wide ranging work undertaken by the previous research work in the larger specialized community and in the local research group (ESRG at

University of Leicester) were reviewed. The underlying aim of the process is to formulate a specific and valid research problem which can add new knowledge to the existing body of knowledge in the domain and can be acknowledged as a novel contribution. The research was focused more towards embedded software development rather than hardware because this played into the prior experience and interest of the author in desktop software development. Following the literature review, group discussions in the research group and personal interest it was agreed that the main direction of the research should be aimed at bringing improvements into the reliability of embedded software architectures. Whilst conducting investigations on this topic at this early stage it was realised that many existing software applications need to be modified and improved during their life cycle in order to improve their reliability. Examples of such applications have already been discussed in CHAPTER 2. For example the F-18 aircraft system discussed in Section 2.2 went through an entire change in the scheduling policy from preemptive to pre-runtime in order to improve reliability. The process to make these changes in the architecture however was extremely tedious for those who were involved in the process and alleviating this problem was seen as a worthy research challenge that would contribute to the existing knowledge in, and progress of, this field of interest. As part of this overall aim of finding ways to make software architectural migration easier, other benefits of improving the system reliability are realized, and another part of the research was involved in evaluating these benefits. The research question then can be articulated as: "Identifying the challenges involved during the migration between different software architectures of complex embedded applications, in

order to improve reliability and to provide an appropriate solution to these challenges".

The research question was further condensed to two primary software architectures as event-triggered (ET) and time-triggered (TT) as various other architectures could be described as subset of these two architectures. Also in the motivating examples described in CHAPTER 2 the existing design of the applications was primarily ET which was transformed to TT in order to improve system reliability and performance.

Having established 'What to do' with the formulation of the research question, there was the next challenge of 'How to do it' in terms of a methodology.

# 3.4. Development of hypothesis and choosing the appropriate methodology

Improving the reliability of embedded systems was central to the research so it was important to investigate what factors contribute to the reliability of an embedded system? In general software organisations focus on the following factors in order to achieve reliable system design:

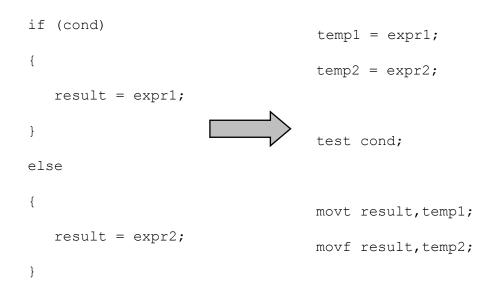

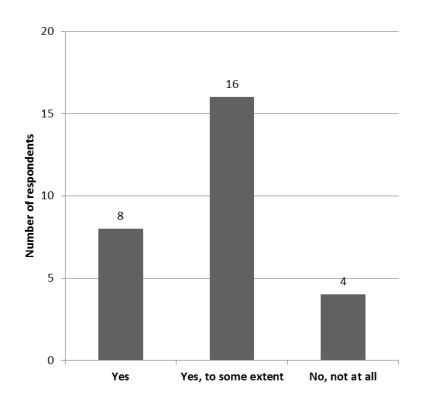

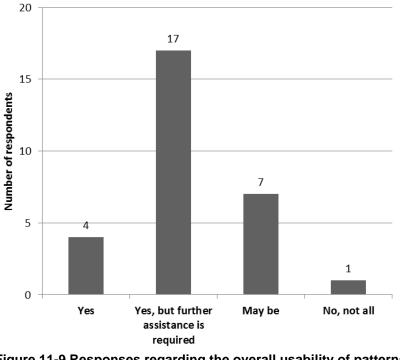

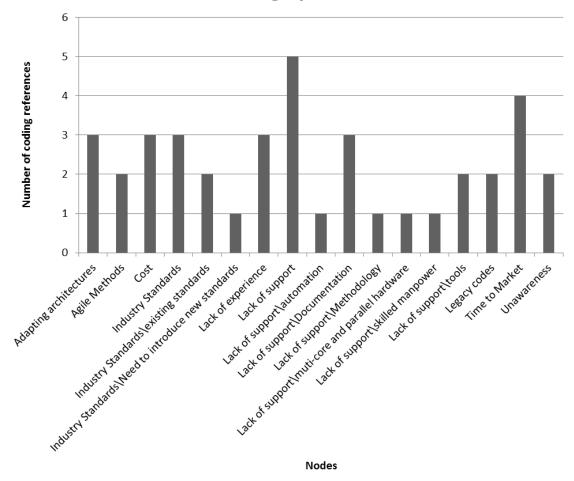

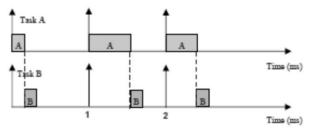

Clear functional requirements: At the system application level the functional requirements (i.e. logic) can be expressed by using semiformal methods such as control flow diagrams or logic/function block diagrams (Liu, 2000).